### **Universidade do Minho**

Escola de Engenharia

Fábio Duarte Rodrigues Magalhães

**Hardware Accelerated Real-Time Linux Video Anonymizer**

**Universidade do Minho** Escola de Engenharia

Fábio Duarte Rodrigues Magalhães

Hardware Accelerated Real-Time Linux Video Anonymizer

**Universidade do Minho** Escola de Engenharia

Fábio Duarte Rodrigues Magalhães

# **Hardware Accelerated Real-Time Linux Video Anonymizer**

Dissertação de Mestrado em Engenharia Eletrónica Industrial e Computadores

Trabalho efetuado sob a orientação do **Professor Doutor Jorge Cabral**

### DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

Licença concedida aos utilizadores deste trabalho

### **Acknowledgements**

I would like to thank all the teachers and colleagues that contributed for my development as an engineer and as a man. But mostly I would like to thank my family for every sacrifice and compromise made, so that I could follow my dreams in the Engineering world.

#### STATEMENT OF INTEGRITY

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

### Resumo

Os Sistemas Embebidos estão presentes atualmente numa variada gama de equipamentos do quotidiano do ser humano. Desde *TV-boxes*, televisões, routers até ao indispensável telemóvel.

O Sistema Operativo *Linux*, com a sua filosofia de distribuição "one-size-fits-all" tornou-se uma alternativa viável, fornecendo um vasto suporte de hardware, técnicas de depuração, suporte dos protocolos de comunicação de rede, entre outros serviços, que se tornaram no conjunto standard de requisitos na maioria dos sistemas embebidos atuais.

Este sistema operativo torna-se apelativo pela sua filosofia *open-source* que disponibiliza ao utilizador um vasto conjunto de bibliotecas de *software* que possibilitam o desenvolvimento num determinado domínio com maior celeridade e facilidade de integração de *software* complexo.

Os algoritmos de *Machine Learning* são desenvolvidos para a automização de tarefas e estão presentes nas mais variadas tecnologias, desde o sistema de foco de imagem no *smartphone* até ao sistema de deteção dos limites de faixa de rodagem de um sistema de condução autónoma.

Estes são algoritmos que quando compilados para as plataformas de sistemas embebidos, resultam num esforço de processamento e de consumo de recursos, como o footprint de memória, que na maior parte dos casos supera em larga escala o conjunto de recursos disponíveis para a aplicação do sistema, sendo necessária a implementação de componentes que requerem maior poder de processamento através de elementos de *hardware* para garantir que as métricas temporais sejam satisfeitas.

Esta dissertação propõe-se, por isso, à criação de um sistema de anonimização de vídeo que adquire, processa e manipula as frames, com o intuito de garantir o anonimato, mesmo na transmissão.

A sua implementação inclui técnicas de Deteção de Objectos, fazendo uso da combinação das tecnologias de aceleração por hardware: paralelização e execução em hardware especializado. É proposta então uma implementação restringida tanto temporalmente como no consumo de recursos ao nível do *hardware* e *software*.

**Palavras-Chave:** Linux Embebido, Deteção de Objectos, Aceleração por Hardware, Machine Learning

**Abstract**

Embedded Systems are currently present in a wide range of everyday equipment. From TV-boxes,

televisions and routers to the indispensable smartphone.

Linux Operating System, with its "one-size-fits-all" distribution philosophy, has become a

viable alternative, providing extensive support for hardware, debugging techniques, network com-

munication protocols, among other functionalities, which have become the standard set of re-

quirements in most modern embedded systems.

This operating system is appealing due to its open-source philosophy, which provides the

user with a vast set of software libraries that enable development in a given domain with greater

speed and ease the integration of complex software.

Machine Learning algorithms are developed to execute tasks autonomously, i.e., without

human supervision, and are present in the most varied technologies, from the image focus system

on the smartphone to the detection system of the lane limits of an autonomous driving system.

These are algorithms that, when compiled for embedded systems platforms, require an ef-

fort to process and consume resources, such as the memory footprint, which in most cases far

outweighs the set of resources available for the application of the system, requiring the imple-

mentation of components that need greater processing power through elements of hardware to

ensure that the time metrics are satisfied.

This dissertation proposes the creation of a video anonymization system that acquires, pro-

cesses, and manipulates the frames, in order to guarantee anonymity, even during the transmis-

sion.

Its implementation includes Object Detection techniques, making use of the combination

of hardware acceleration technologies: parallelization and execution in specialized hardware.

An implementation is then proposed, restricted both in time and in resource consumption at

hardware and software levels.

**keywords:** Linux, Object Detection, Hardware Acceleration

İν

## **Table of Contents**

| Re  | sumo    | )        |                                    | iii |

|-----|---------|----------|------------------------------------|-----|

| Αb  | strac   | t        |                                    | iv  |

| Lis | st of L | istings  |                                    | xiv |

| Ac  | ronyr   | ns List  |                                    | χv  |

| 1   | Intro   | oductio  | n                                  | 1   |

|     | 1.1     | Contex   | tualization                        | 1   |

|     | 1.2     | Motivat  | tion and Goals                     | 4   |

|     | 1.3     | Contrib  | outions                            | 4   |

|     | 1.4     | Dissert  | ation Structure                    | 4   |

| 2   | The     | oretical | Foundations                        | 6   |

|     | 2.1     | Embed    | lded System                        | 6   |

|     |         | 2.1.1    | Generic Embedded System's Hardware | 7   |

|     |         | 2.1.2    | Storage                            | 8   |

|     |         | 2.1.3    | Real-Time Systems                  | 8   |

|     | 2.2     | Compu    | ıter Architecture                  | 10  |

|     |         | 2.2.1    | Data-Level Parallelism             | 10  |

|     |         | 2.2.2    | Instruction-Level Parallelism      | 11  |

|     |         | 2.2.3    | Pipeline                           | 12  |

|     |         | 2.2.4    | Cache                              | 13  |

|     | 2.3     | Data R   | epresentation                      | 14  |

|     |         | 2.3.1    | Floating-Point Representation      | 14  |

|     |         | 232      | Fixed Point Representation         | 16  |

|      | 2.3.3    | Quantization                     | 16 |

|------|----------|----------------------------------|----|

| 2.4  | Linux ar | nd Embedded Systems              | 18 |

|      | 2.4.1    | Embedded Linux                   | 18 |

|      | 2.4.2    | Linux and Memory Management      | 20 |

|      | 2.4.3    | Linux and Real-Time applications | 21 |

|      | 2.4.4    | Latency                          | 21 |

|      | 2.4.5    | Preemption                       | 22 |

|      | 2.4.6    | Real-Time Kernel Patch           | 23 |

| 2.5  | Image P  | Processing                       | 24 |

|      | 2.5.1    | Image Decoding                   | 24 |

|      | 2.5.2    | Color Space Conversion           | 26 |

|      | 2.5.3    | Image Resize                     | 26 |

|      | 2.5.4    | Normalization                    | 29 |

|      | 2.5.5    | Gaussian Function                | 31 |

| 2.6  | Machine  | e Learning                       | 31 |

|      | 2.6.1    | Feature                          | 32 |

|      | 2.6.2    | Feature Descriptor               | 32 |

|      | 2.6.3    | Supervised Learning              | 32 |

|      | 2.6.4    | Unsupervised Learning            | 33 |

|      | 2.6.5    | Computer Vision                  | 34 |

| 2.7  | Histogra | nm of Oriented Gradients         | 34 |

|      | 2.7.1    | Image Gradients                  | 35 |

| 2.8  | Support  | Vectors Machine                  | 37 |

|      | 2.8.1    | Support Vectors                  | 37 |

|      | 2.8.2    | Linear Classification            | 38 |

| 2.9  | Hardwa   | re Acceleration                  | 39 |

|      | 2.9.1    | Hardware Descriptor Languages    | 39 |

|      | 2.9.2    | FPGA                             | 42 |

| 2.10 | Hardwa   | re-Software Co-Design            | 44 |

|      | 2.10.1   | System Modeling                  | 44 |

|      | 2 10 2   | Software Parallelization         | 44 |

|   |       | 2.10.3    | Profiling                                 | 44 |

|---|-------|-----------|-------------------------------------------|----|

|   |       | 2.10.4    | Hardware Design                           | 45 |

|   |       | 2.10.5    | Validation                                | 45 |

|   |       | 2.10.6    | Metrics Confirmation/Implementation       | 45 |

|   | 2.11  | Hardwa    | re Accelerated Embedded System Simulation | 46 |

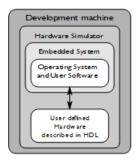

|   |       | 2.11.1    | Full System RTL Simulation                | 46 |

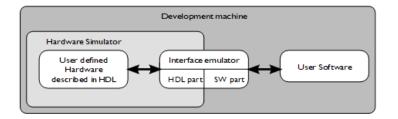

|   |       | 2.11.2    | RTL Simulation with Host Software         | 47 |

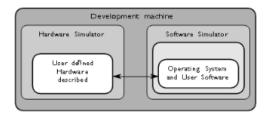

|   |       | 2.11.3    | RTL-Software Co-Simulation                | 47 |

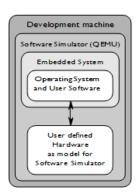

|   |       | 2.11.4    | Full System Software Simulation           | 48 |

| 3 | Syste | em Desi   | gn                                        | 49 |

|   | 3.1   | Detection | on System                                 | 49 |

|   | 3.2   | HARVA     | System                                    | 50 |

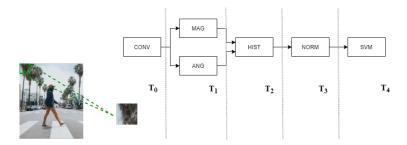

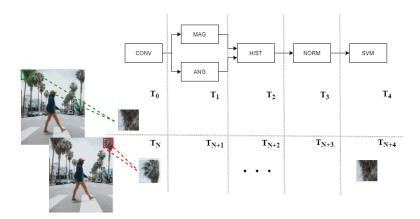

|   |       | 3.2.1     | HOG                                       | 54 |

|   |       | 3.2.2     | SVM                                       | 56 |

|   | 3.3   | HOG Fe    | eatures Extraction                        | 58 |

|   |       | 3.3.1     | Convolution Stage                         | 59 |

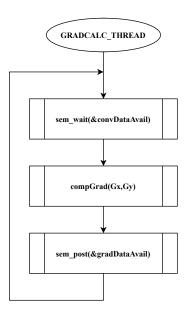

|   |       | 3.3.2     | Gradient Calculation Stage                | 60 |

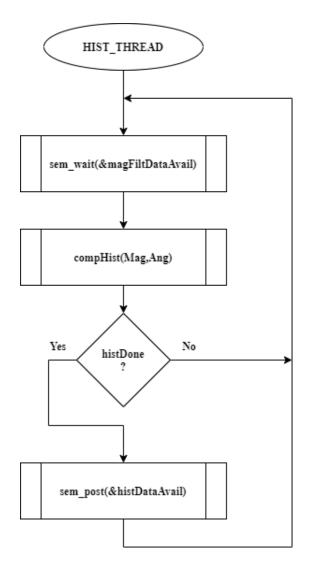

|   |       | 3.3.3     | Histogram Stage                           | 63 |

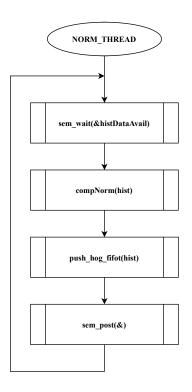

|   |       | 3.3.4     | Normalization Stage                       | 64 |

|   |       | 3.3.5     | Component Parallelism                     | 66 |

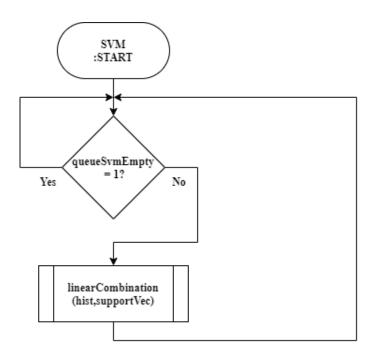

|   | 3.4   | SVM Cla   | assification                              | 66 |

|   |       | 3.4.1     | Quantization Stage                        | 68 |

|   |       | 3.4.2     | Linear Combination Stage                  | 68 |

|   |       | 3.4.3     | Component Parallelism                     | 69 |

| 4 | Expe  | rimenta   | al Results                                | 71 |

|   | 4.1   | Test Er   | nvironment                                | 71 |

|   |       | 4.1.1     | Hardware                                  | 73 |

|   |       | 4.1.2     | Communication Interfaces                  | 74 |

|   |       | 4.1.3     | Testbench                                 | 75 |

|   | 4.0   | Toot Co.  |                                           | 76 |

| D. | foron | 000              |                          | 102      |

|----|-------|------------------|--------------------------|----------|

|    | 5.2   | Future V         | Work                     | 95       |

|    | 5.1   | Develop          | ped Work                 | 94       |

| 5  | Cond  | clusion          |                          | 94       |

|    |       | 4.5.2            | Detection Rate           | 93       |

|    |       | 4.5.1            | False Detection          | 92       |

|    | 4.5   |                  | on Performance           | 92       |

|    | 4 -   | 4.4.3            | SVM Component            | 91       |

|    |       | 4.4.2            | HOG Component            |          |

|    |       |                  | Software Model Profiling | 89       |

|    | 4.4   | Results<br>4.4.1 | Coffware Model Drefiling | 87<br>87 |

|    | 4.4   | 4.3.3            | SVM Thread               | 86       |

|    |       | 4.3.2            | HOG Thread               | 82       |

|    |       | 4.3.1            | Preprocessing Thread     | 81       |

|    | 4.3   |                  | e Model Architecture     | 80       |

|    |       | 4.2.4            | Detecting Window         | 79       |

|    |       | 4.2.3            | Cache Miss               | 78       |

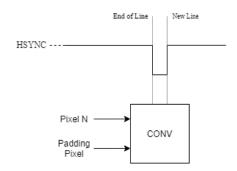

|    |       | 4.2.2            | HSYNC                    | 77       |

|    |       | 4.2.1            | Block Diagram            | 76       |

## **List of Figures**

| 1.1 | Embedded System's wide range of applications in modern technology                                         | 2  |

|-----|-----------------------------------------------------------------------------------------------------------|----|

| 1.2 | Machine Learning several application areas in technology                                                  | 3  |

| 2.1 | The Engine Control Unit, introduced in 1970, plays a fundamental role in en-                              |    |

|     | suring the optimal performance of the automobile                                                          | 7  |

| 2.2 | Composition of a Real-Time Embedded System                                                                | 10 |

| 2.3 | Vector Architecture designed to support the processing of several blocks of data                          |    |

|     | within the multiple Processing Element(PE) implemented. Vector Architectures                              |    |

|     | provide an higher throughput at the expense of more hardware for concurrent                               |    |

|     | processing                                                                                                | 11 |

| 2.4 | Simple RISC pipeline designed for a five-cycle instruction executed. The pro-                             |    |

|     | cessor performance is increased by five times, compared with a processor not                              |    |

|     | pipelined. The pipeline is defined within the stages: $IF = instruction fetch$ , $ID = instruction fetch$ |    |

|     | instruction decode, EX = execution, MEM = memory access, and WB =write-back.                              | 12 |

| 2.5 | Memory hierarchy in modern Computer Systems, targeting a more optimized                                   |    |

|     | data access through implementation of faster and smaller memories between                                 |    |

|     | the processor and the Main Memory.                                                                        | 13 |

| 2.6 | Single Precision Floating Point representation, as defined by the IEEE Standard                           |    |

|     | for Floating-Point Arithmetic.                                                                            | 15 |

| 2.7 | Double Precision Floating Point representation as defined by the IEEE Standard                            |    |

|     | for Floating-Point Arithmetic.                                                                            | 15 |

| 2.8 | The graphic on the left side shows the voltage applied to and ADC, ranging from                           |    |

|     | 0V to 10V. The graphic on the right side shows the the quantization results for                           |    |

|     | the different possible values applied to the ADC.                                                         | 18 |

| 2.9 | Importance of connectivity in modern devices                                                              | 19 |

| 2.10 | Layer hierarchy for device access in Linux OS                                          | 20 |

|------|----------------------------------------------------------------------------------------|----|

| 2.11 | Real-Time system response to a critical event                                          | 22 |

| 2.12 | Detailed Real-Time system's response to a critical event                               | 22 |

| 2.13 | Image perception by a playback device. The synchronization signals dictate the         |    |

|      | active are of the image                                                                | 25 |

| 2.14 | The graph (a) describes the disposition of negatively skewed data, with the me-        |    |

|      | dian and mode placed on the right side of the mean value. Graph (b) describes          |    |

|      | data disposition without skew, which mean, mode and median values are the              |    |

|      | same. Graph (c) describes the disposition of positively skewed data, where the         |    |

|      | median and mode are placed on the left side of the mean value                          | 30 |

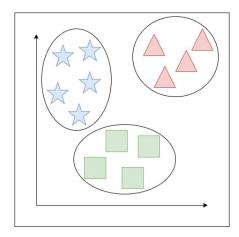

| 2.15 | Machine Learning Classification problem.                                               | 33 |

| 2.16 | Machine Learning Regression problem                                                    | 33 |

| 2.17 | Machine Learning Clustering problem                                                    | 34 |

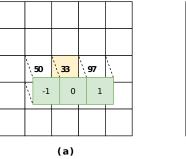

| 2.18 | The Convolution is applied in the horizontal, (a), and vertical directions, (b) of the |    |

|      | image. The target pixel, represented in yellow, is centered with the convolution       |    |

|      | kernel and the neighbors are subtracted, calculating the derivative                    | 36 |

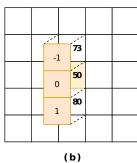

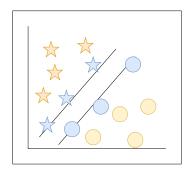

| 2.19 | The graph represents the distribution of two different classes of data, balls and      |    |

|      | stars. The blue points represent the support vectors, mapped the closest to the        |    |

|      | separating gap                                                                         | 37 |

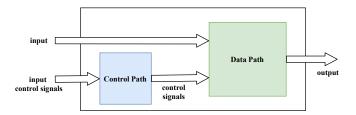

| 2.20 | Block diagram of a general HDL module, representing the interaction between            |    |

|      | the Control and Data path.                                                             | 40 |

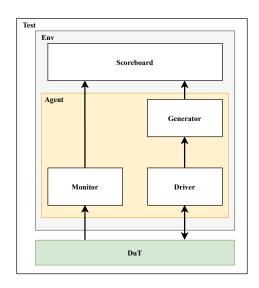

| 2.21 | Architecture of a UVM-based testbench for validation of HDL designs                    | 41 |

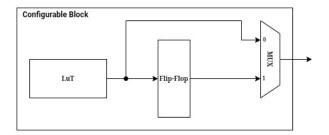

| 2.22 | Basic configurable block present in FPGA fabric                                        | 42 |

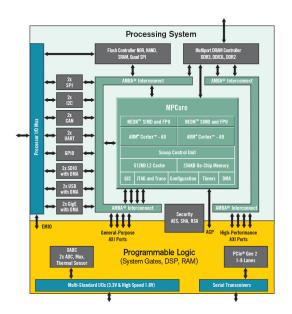

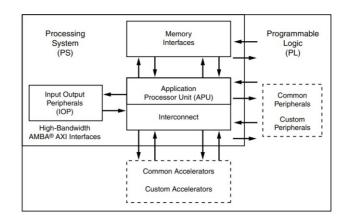

| 2.23 | Zynq-7000 SoC's block diagram.                                                         | 43 |

| 2.24 | Full system RTL simulation diagram.                                                    | 47 |

| 2.25 | RTL simulation with host software diagram.                                             | 47 |

| 2.26 | RTL-Software co-simulation diagram.                                                    | 48 |

| 2.27 | Full system software simulation diagram.                                               | 48 |

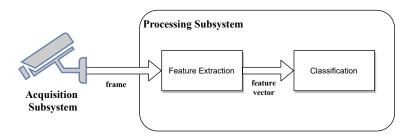

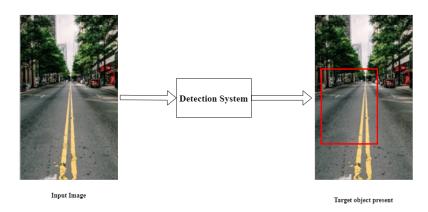

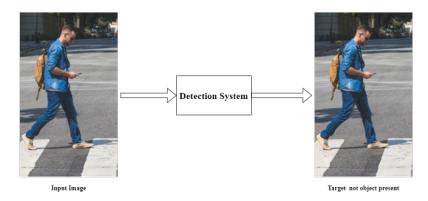

| 3.1  | General architecture for a Detection System. The system is mainly divided              |    |

|      | between the Acquisition and the Processing of the surrounding environment's            |    |

|      | data                                                                                   | 50 |

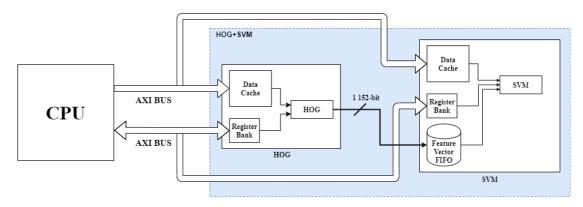

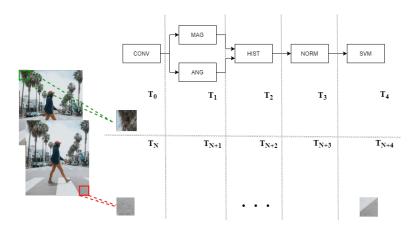

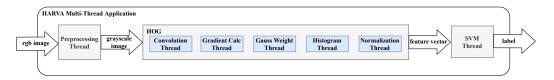

| 3.2  | High-Level Block Diagram view of the HARVA system.                                | 51 |

|------|-----------------------------------------------------------------------------------|----|

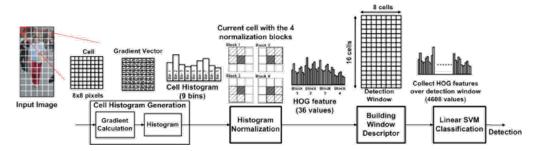

| 3.3  | HARVA system divides the input image within several subsets, computing for        |    |

|      | each the intensity variation in a form of an histogram.                           | 51 |

| 3.4  | Grayscale transformation routine for Image Processing applications                | 51 |

| 3.5  | Detecting Window algorithm for multiple locations detection                       | 52 |

| 3.6  | Image Pyramid algorithm for multiple scale detection                              | 52 |

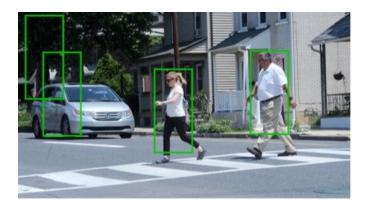

| 3.7  | Multiple Pedestrian Detection                                                     | 53 |

| 3.8  | Bluring filter for anonymization of target object in Object Detection algorithms. | 53 |

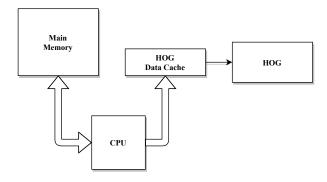

| 3.9  | HOG's components 2-level memory hierarchy                                         | 54 |

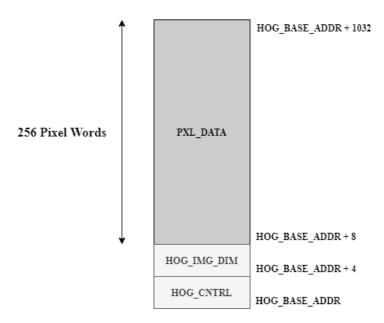

| 3.10 | HOG's components Data Cache memory layout. The memory is divided in               |    |

|      | several section for the different required accesses                               | 55 |

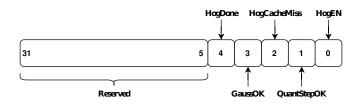

| 3.11 | HOG CONTROL register bit description.                                             | 56 |

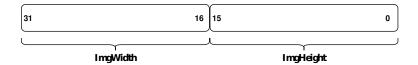

| 3.12 | IMG_DIM register bit description.                                                 | 56 |

| 3.13 | HOG's components Data Cache memory layout. The memory is divided in               |    |

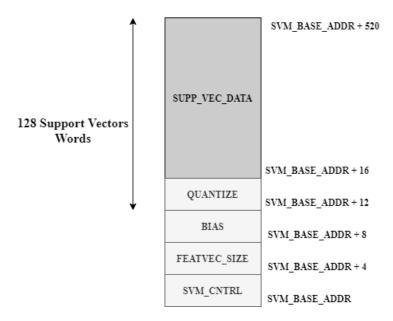

|      | several section to support the different required accesses                        | 57 |

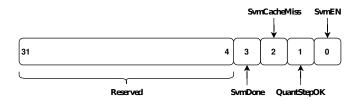

| 3.14 | SVM CONTROL register bit description.                                             | 57 |

| 3.15 | HOG component's block diagram. The component is designed as a 4-stage             |    |

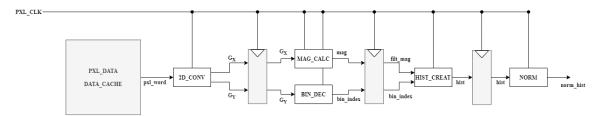

|      | pipeline, aiming an increased data throughput.                                    | 58 |

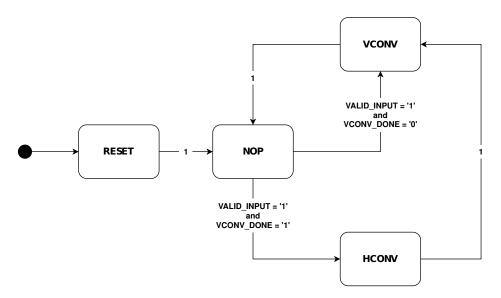

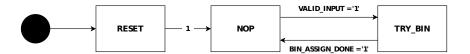

| 3.16 | $2D\_CONV$ component's state machine                                              | 59 |

| 3.17 | Block Diagram of the logic implemented for the computation of each value of       |    |

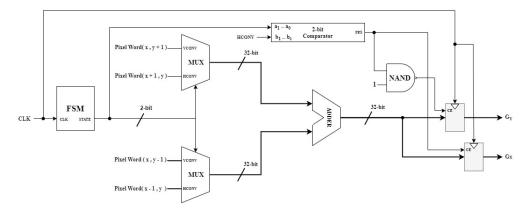

|      | the $G_x$ and $G_y$ derivatives                                                   | 60 |

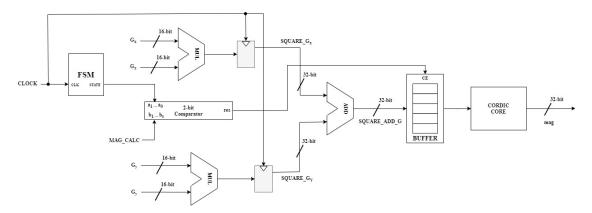

| 3.18 | $MAG\_CALC$ block diagram, illustrating the pipeline behavior implemented         |    |

|      | for the Magnitude Gradient computation.                                           | 61 |

| 3.19 | $MAG\_CALC$ component's state machine                                             | 61 |

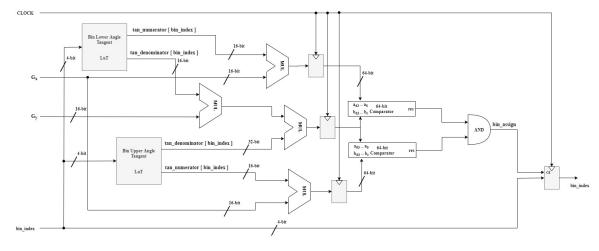

| 3.20 | $BIN\_CALC$ component's block diagram                                             | 62 |

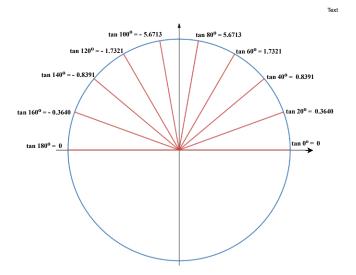

| 3.21 | Tangent's trignometric upper half of the unit circle                              | 63 |

| 3.22 | $BIN\_CALC$ component state machine                                               | 63 |

| 3.23 | $HIST\_CREAT$ component's state machine                                           | 64 |

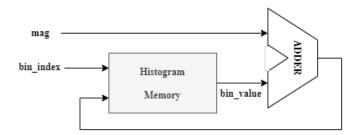

| 3.24 | $HIST\_CREAT$ component's block diagram, illustrating the histogram up-           |    |

|      | date operation                                                                    | 64 |

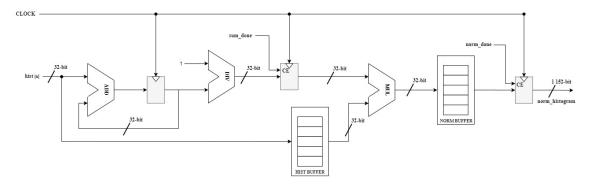

| 3.25 | Block Histogram Normalization Stage's block diagram. The red signal symbol-                                           |    |

|------|-----------------------------------------------------------------------------------------------------------------------|----|

|      | ize the control signal generated by the Control Path to manipulate the behavior                                       |    |

|      | of the implemented modules. The blue signals represent the signals that im-                                           |    |

|      | pact the control signals generation. The green signals are used to represent the                                      |    |

|      | data manipulated within the stage.                                                                                    | 65 |

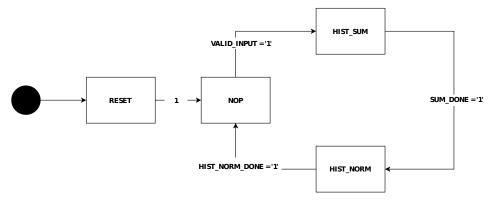

| 3.26 | $HIST\_NORM$ component's state machine                                                                                | 65 |

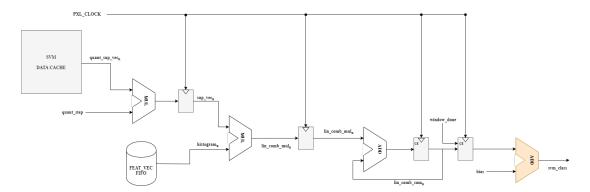

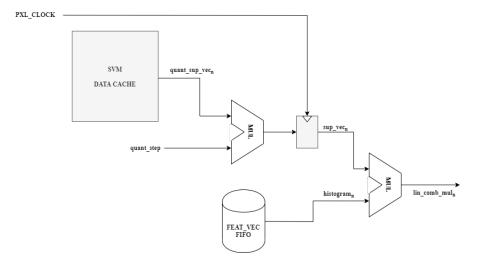

| 3.27 | SVM component's block diagram. The red signal symbolize the control signal                                            |    |

|      | generated by the Control Path to manipulate the behavior of the component.                                            |    |

|      | The blue signals represent the signals that impact the control signals value. The                                     |    |

|      | green signals are used to represent the data manipulated within the $SVM. \ \ .$                                      | 67 |

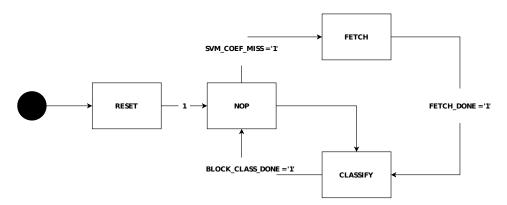

| 3.28 | SVM component's state machine                                                                                         | 67 |

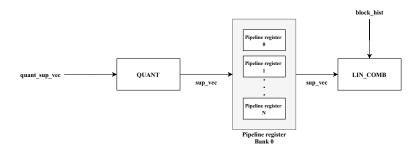

| 3.29 | QUANT component's block diagram                                                                                       | 68 |

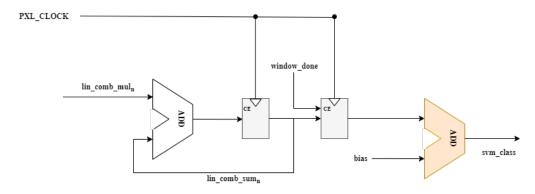

| 3.30 | $LIN\_COMB$ component's block diagram                                                                                 | 69 |

| 3.31 | $SVM$ component's implementation as a two-stage pipeline, targeting increased $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |    |

|      | throughput by exploiting data-parallelism                                                                             | 70 |

| 4.1  | Vivado Simulator flow for HDL development                                                                             | 72 |

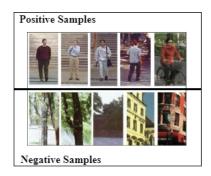

| 4.2  | Example of INRIA dataset positive samples                                                                             | 73 |

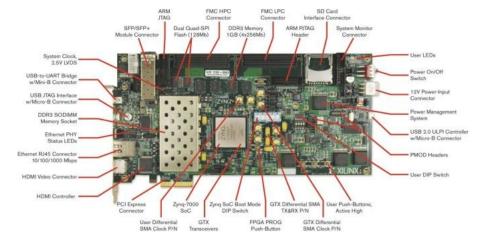

| 4.3  | ZC706 Evaluation Board                                                                                                | 73 |

| 4.4  | ZC706 Evaluation Board High-Level Block Diagram                                                                       | 74 |

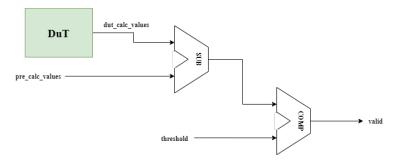

| 4.5  | Fixed-Point error compensation hardware                                                                               | 76 |

| 4.6  | Block Diagram test case for the INRIA dataset                                                                         | 77 |

| 4.7  | HSYNC event for the HARVA system                                                                                      | 77 |

| 4.8  | HSYNC test case for the INRIA dataset                                                                                 | 78 |

| 4.9  | Detecting Window test case for the INRIA dataset                                                                      | 79 |

| 4.10 | Object detection application as Pipeline multi-threaded Model                                                         | 80 |

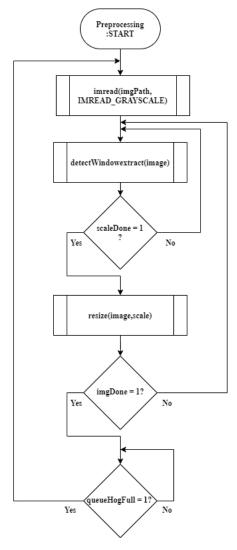

| 4.11 | Preprocessing component flowchart for the HARVA system                                                                | 81 |

| 4.12 | imread API's documentation.                                                                                           | 82 |

| 4.13 | OpenCV <i>resize</i> 's documentation                                                                                 | 82 |

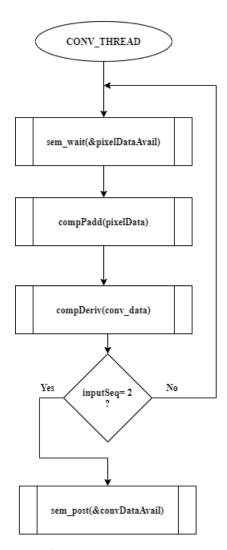

| 4.14 | Convolution Stage software implementation for the HARVA's profiling                                                   | 83 |

| 4.15 | Gradient Calculation Stage software implementation for the HARVA profiling                                            | 84 |

| 4.16 | Histogram Stage software implementation for the HARVA profiling                                                       | 85 |

| 4.17 | Normalization Stage software implementation for the HARVA profiling              | 86 |

|------|----------------------------------------------------------------------------------|----|

| 4.18 | SVM thread's diagram                                                             | 87 |

| 4.19 | Oprofile results for the profiling of the HARVA software implementation          | 88 |

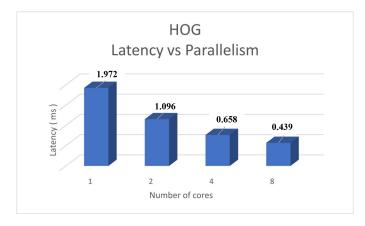

| 4.20 | Hardware profiling chart for the HOG HDL design. The chart provides informa-     |    |

|      | tion about the latency variation for different number of cores configurations of |    |

|      | the HOG                                                                          | 89 |

| 4.21 | HOG HDL design's synthesis results.                                              | 90 |

| 4.22 | HOG HDL design's synthesis results for DSP slices                                | 90 |

| 4.23 | HOG HDL design's synthesis results for BRAM blocks                               | 90 |

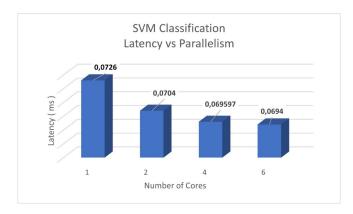

| 4.24 | Hardware profiling chart for the SVM HDL design. The chart provides informa-     |    |

|      | tion about the latency variation for different number of cores configurations of |    |

|      | the SVM                                                                          | 91 |

| 4.25 | HOG HDL design's synthesis results.                                              | 91 |

| 4.26 | HOG HDL design's synthesis results for BRAM blocks                               | 92 |

| 4.27 | False Positives within a Object Detection System.                                | 92 |

| 4.28 | False Negatives within a Object Detection System.                                | 93 |

## **List of Equations**

| 2.1 Conversion from IEEE Floating Point to Real number                               | 15 |

|--------------------------------------------------------------------------------------|----|

| 2.2 Uniform Step size formula                                                        | 17 |

| 2.3 Uniform Quantization formula                                                     | 17 |

| 2.4 Image scaling formula                                                            | 27 |

| 2.5 Pixel Selection formula                                                          | 28 |

| 2.6 L1 Normalization formula                                                         | 30 |

| 2.7 Gaussian Function formula                                                        | 31 |

| 2.8 Convolution kernels for computation of image Horizontal and Vertical derivatives | 36 |

| 2.9 Image Magnitude Gradient formula                                                 | 36 |

| 2.10Image Angle Gradient formula                                                     | 36 |

| 2.11SVM formula for mapping new data point into the its hyperplanes                  | 38 |

| 2.12SVM formula for classification of new data points                                | 38 |

| 3.1 XILINX CORDIC Fixed Point converting factor                                      | 61 |

| 3.2 Bin assignment formula                                                           | 62 |

| 3.3 Extended Bin assignment formula                                                  | 62 |

| 3.4 I 1 Norm multiplication factor.                                                  | 65 |

### **Acronyms List**

**ADC** Analog-to-Digital Converter.

**ALU** Arithmetic Logic Unit.

**API** Application Programming Interface.

**ASIC** Application Specific Integrated Circuit.

**AXI** Advanced eXtensible Interface.

**BRAM** Block Random-Access Memory.

**CORDIC** COordinate Rotation Digital Computer.

**CPU** Central Processing Unit.

**DLP** Data-Level Paralellism.

**DMA** Direct Memory Access.

**FIFO** First In First Out.

FPGA Field-Programmable Gate Array.

FPU Floating-Point Unit.

**GPL** General Public License.

**GPU** Graphics Processing Unit.

**HARVA** Hardware Accelerated Real-Time Linux Video Anonimyzer.

**HDL** Hardware Description Languages.

**HOG** Histogram of Oriented Gradients.

**HSYNC** Horizontal Synchronization.

**IEEE** Institute of Electrical and Electronics Engineers.

**ILP** Instruction-Level Parallelism.

**INRIA** Institut National de Recherche en Informatique et en Automatique.

**IP** Intellectual property.

**LuT** Look-Up Table.

MMU Memory Management Unit.

**OS** Operating System.

**PLD** Programmable Logic Device.

**POSIX** Portable Operating System Interface.

**RAM** Random-Access Memory.

RTL Register-Transfer Level.

**RTOS** Real-Time Operating System.

**SIMD** Single Instruction Multiple Data.

SoC System On Chip.

**SVM** Support Vector Machine.

VHDL Very High Speed Integrated Circuits Hardware Description Language.

**VSYNC** Vertical Synchronization.

YOLO You Only Look Once.

### **Chapter 1**

### Introduction

In this chapter the Hardware Accelerated Real-Time Linux Video Anonimyzer (HARVA) Dissertation's scope and goals are addressed, as well as the motivation for the development of the proposed system.

The chapter is concluded with an brief explanation of the document's organization and the contents addressed.

### 1.1 Contextualization

Embedded Systems are an aspect of Computer Systems technologies, presenting themselves as an efficient solution where both software and hardware are co-designed, aiming the optimization of the SWaP-C (Size, Weight, Power and Cost) metrics.

This is a challenging task and one that requires a great knowledge of the technologies present in the system, requiring research and in-depth study, presenting itself as an great source of technological development.

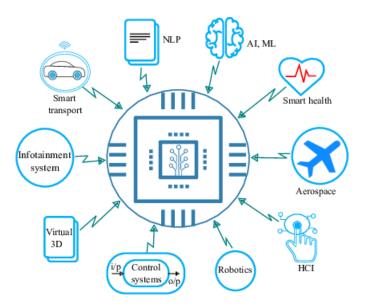

Embedded systems have gained importance with the growth of technology, evolving from bare metal applications to fully supporting Operating System (OS)s and complex software, as depicted in the figure 1.1. [1]

Figure 1.1: Embedded System's wide range of applications in modern technology.

Modern technology is developed for increasingly complex systems, with the rising of concepts such as Internet of Things and Industry 4.0 boosting a demand for connectivity and intelligence in a great variety of devices. The everyday life of the human being is full of smart technological devices, from smart appliances, which facilitate the home chores, to the more complex systems such as autonomous driving. The exponential growth of technology has also boosted the industry, with the implementation of production lines mainly controlled by robotics systems, increasing the daily number of units produced.

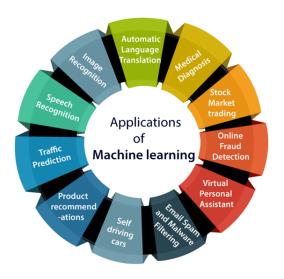

Machine Learning algorithms are designed to enable the realization of human tasks, using surrounding environment data to make decisions independently.[2] This algorithms are present in almost every device and industries, as represented in figure 1.2.[3] One popular Machine Learning problem is the Object Detection in images, or video streaming, implemented by several devices used on a daily basis, such as in the smartphone for image focus.

Figure 1.2: Machine Learning several application areas in technology.

The porting of Machine Learning algorithms to Embedded Systems is a challenging task, due to the high complexity and computational cost associated with these algorithms and the fact that these systems present limitations in terms of memory and performance, which are two key factors for Machine Learning applications. A pure software implementation might present itself as not reliable, or even feasible for more constrained systems. The solution is to develop the software application in the host system, where all resources are available to execute the algorithm normally, and analyze its behavior for bottlenecks, i.e., parts of the algorithm which are limiting the performance. After the analysis of the application, the most computational demanding parts of the algorithm are implemented as hardware components, decreasing the latency and the dependency of the CPU performance. In terms of memory requirements, there are multiple solutions provided by open source libraries to tackle this problem, either by decreasing the coefficients required or by mapping the Floating Point values to smaller integers.

In this Digital Age where personal information is used as a major currency for companies, which gather all sorts of data about to wide its customer base, even systems designed to a simpler task can be used to compute important data. Object Detection Systems can be exploited to trace which day and hour has the most people on the set area, an important data for possible investors interested in creating a business in the same area. In the same manner, Detection Systems targeting pedestrians might be used to gather the identification of the persons, by storing the detected images and run a recognition software. Anonymity in this Digital Age is

fundamental for the protection of human rights, providing safety and privacy. ref[https://digital-rightswatch.org.au/2021/04/30/explainer-anonymity-online-is-important/]

### 1.2 Motivation and Goals

Embedded Systems was always the major area of interest of the author since the start of his academic path. The possibility to combine Embedded System and Machine Learning, which is one of the most popular topics in current technology, sparked great interest and joy from the author. Porting the Linux OS to embedded systems enabled faster software development, due to the availability of several open source libraries targeting a vast range of applications, such as robotics and mobile devices.

The possibility of using open source implementations, which offer several solutions for problems across a wide range of areas, increased the importance of intelligence and connectivity in modern devices. One of the areas that benefited most with this demand was Computer Vision, which is used in a wide range of systems for several applications.

The development of software and hardware components to produce efficient solutions covers all the necessary skills for modern engineering requirements.

### 1.3 Contributions

This dissertation addresses the development process of an Embedded System and the challenges an engineering team is presented with.

The hardware components were designed to enable several levels of parallelism, i.e., a different number of values processed in parallel, providing the user the possibility to choose a design more latency or resource-oriented, and to enable different configurations without requiring major changes in the implemented Register-Transfer Level (RTL).

### 1.4 Dissertation Structure

This dissertation addresses the development of the Hardware Accelerated Real-Time Linux Video Anonimyzer system and is structured into five chapters, which will be explained in this section.

The Introduction chapter provides an introduction to the dissertation as well as motivation and main contributions.

The second chapter addresses the theoretical foundations necessary for the development of a Linux-based Embedded System and the required modifications to the kernel for targeting real-time applications. A light introduction to Machine Learning and Computer Vision areas is included to promote the necessary knowledge for understanding the developed system. The chapter finishes with topics regarding hardware development through Hardware Description Languages (HDL) and the several available methodologies to test a system with software and HDL modules.

The third chapter details the implemented system and the decisions on which its development was based. The possible configurations for the developed modules are discussed and the advantages and disadvantages are explained. The interfaces between the software and the HDL components are also addressed.

The fourth chapter presents the case of study for the HARVA system, which is based on a popular dataset in the Computer Vision community targeting pedestrian detection. The chapter finishes with a discussion of the results from the software and HDL implementations and the conclusions taken by the author related to the developed work.

The fifth chapter addresses the developed work for the HARVA system focusing on the conclusions, and evaluates possibilities of future work.

### **Chapter 2**

### **Theoretical Foundations**

This chapter addresses the technology and concepts used in the development of the HARVA, starting with the definition of Embedded Systems and their placement in the real-time spectrum.

Concepts from the Computer Architecture area supporting the system's memory hierarchy and data parallelism are addressed for support of the system implementation in the later chapters.

Linux is introduced with an examination of the key features that make it the developer's choice for the OS in embedded systems, as well as the necessary modifications to make it suitable for Real-Time applications.

A light introduction to Machine Learning and Image Processing is included, explaining the different algorithms and their applications. This information is useful for a better understanding of the system developed.

The chapter finishes with the description of the Hardware-Software Co-Design methodology and the processes associated with the development of user-defined hardware.

### 2.1 Embedded System

Embedded systems are computers designed in hardware and software to meet specific constraints, targeting the realization of a specific task within a bigger system.

Embedded systems are optimized solutions for size and power consumption and increase the system's reliability and performance.

These systems are present in a wide range of devices, from portable ones like the popular smartwatches to more complex systems like the Engine Control Unit present in every modern automobile, represented in the figure 2.1.[4]

**Figure 2.1:** The Engine Control Unit, introduced in 1970, plays a fundamental role in ensuring the optimal performance of the automobile.

### 2.1.1 Generic Embedded System's Hardware

An Embedded System is designed for a specific use case, implementing only the necessary components for the task realization. Some components are generic for a wide range of applications, providing core functionalities. These components are dimensioned to fit the needs and constraints of the target system.

The generic components present in almost every computer system are:

- CPU Responsible for fetching, decoding and executing the programmed instructions that

comprise the user-defined application. Multiple architectures are available in the market

suitable for different use cases. This unit is the key factor to both the system's power

consumption and instruction throughput, requiring a well-thought tradeoff;

- Memory banks Logical units of data storage used in electronics devices. In most computers, there are two types of memory present: Volatile and Non-Volatile. Volatile memories require power to retain the stored data and are used for the heap and the stack of the different software components. Non-Volatile Memories retain the stored data even if power off event happens, which is why it is used for storing the application code as well as constant data.

- Real-Time Clock Precise integrated circuit that runs independently of the CPU and is essential for any device that needs accurate time functionalities;

Communication ports - Essential for communication with external devices, such as sensors or monitoring systems.

Computers often use processors, which together with the CPU implement hardware components designed for specific tasks. One popular example, present in most modern computers, is the Direct Memory Access (DMA) designed for handling data exchange between different components within the system. The same concept is applied to hardware accelerators, where a task is implemented as a user-defined hardware component and integrated into the processor.

#### 2.1.2 Storage

In embedded systems, the storage capacity is dimensioned to meet the needs of the system, due to a decreased need for storage when compared with other computers. The hard drive solution, which is the solution for computers where large blocks of data are needed to be stored, is not optimal for embedded applications since only a small part of the available storage would be used.

Using hard drives for storage in embedded systems would also be impracticable since these systems are often required to be of reduced volume and power consumption.

In most Embedded Systems Flash memories are used since this technology is available in smaller storage sizes and volume, provide better power efficiency, consuming around 50% less than the Hard drive solution, and greater robustness, i.e., less prone to physical damage and unexpected failures, which is fundamental for critical applications [5].

The Flash solution is also beneficial in terms of memory access latency, providing faster read/write operation than the Hard drive implementation.

#### 2.1.2.1 Flash Memory

#### 2.1.3 Real-Time Systems

Real-Time systems are computer systems that operate by strict timing constraints within it must acknowledge and handle critical events. Real-Time applications must be implemented respecting the core concepts of Functional and Time correctness [6].

Functional correctness requires that all computations must be precise and correct, even if it implies that the logic implemented is less efficient. Data integrity is more important than the system throughput.

Time correctness defines a time frame within which all necessary computations must be concluded. If the time frame is not respected, the data is considered compromised and discarded.

Real-time systems can be classified into two types: Hard and Soft Real-Time. The difference between a Hard and a Soft Real-Time System lies in the severity of the consequences of missing a deadline [7].

In Hard Real-Time systems violating the time frame means catastrophe and can result in great economic damage, or the worst-case scenario in the loss of lives. One example of a Hard Real-Time system is the braking system used in the automotive and aircraft industries, which must ensure that the system actuates within a stipulated time or else the safety of the passengers is liable to danger.

In Soft Real-Time applications, missing a deadline does not endanger the user or the system itself. This scenario can present itself as economic damage as well, due to customer dissatisfaction. A common example of Soft Real-Time Systems is the multimedia applications, like the video players present in every streaming platform, where the consequence of missing the timing deadline is the user experiencing lag in the video reproduction, which can be very unpleasant but not dangerous in any kind.

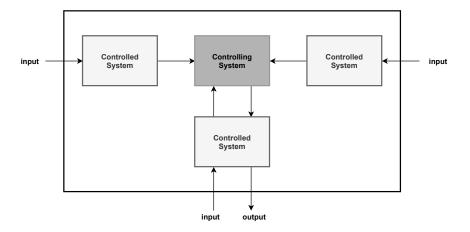

The structure of a Real-Time system [6] is composed of two types of components, as it is depicted in figure 2.2.

The Controlling component is responsible for acknowledging and handling the Controlled components, whose function is to interact with the external environment and raise an event when certain conditions are met.

The communication between the controlling and controlled components can be done in two manners:

- Periodic The communication is initiated by the controlling system, pooling every controlled component for events raised. The interaction is predictable and the execution flow of the controlling components is not interrupted;

- Aperiodic The communication is initiated by the controlled component, through interrupt

or events raised, and impose the immediate handling to the controlling system. This type

of interaction, if poorly designed, might compromise the system due to the possibility of a

high frequency of events raised, which can happen on a defective component.

Figure 2.2: Composition of a Real-Time Embedded System.

Real-time systems are denominated deterministic because the response time to a specific and critical event is bounded and known before the implementation.

The levels of determinism and robustness of a system have to be balanced because a highly deterministic system is less adjustable to a mutable environment, therefore becoming less robust.

### 2.2 Computer Architecture

Computer Engineering is the branch of engineering directed to the development of computer hardware and software, integrating multiple fields of Computer Science, which studies algorithmic processes and computational systems, and Electrical and Electronic Engineering, a discipline oriented to the development of electronic devices.

In Computer Engineering, Computer Architecture is the design of a computational system through a set of rules and criteria describing the functionality, organization and implementation of a computer. This process involves the analysis of the necessary attributes for the computer and the maximization of the performance and energy efficiency while remaining within a price range.

#### 2.2.1 Data-Level Parallelism

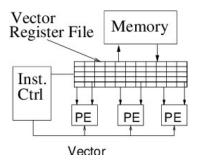

Data-Level Paralellism (DLP) is the concept of distributing blocks of data within different processing elements within the system, decreasing the overall latency of the operation through the increment of the system's parallelism. Modern processors implement Vector Architectures, represented in figure 2.3[8], to process instructions, or operations, in several blocks of data concurrently.

**Figure 2.3:** Vector Architecture designed to support the processing of several blocks of data within the multiple Processing Element(PE) implemented. Vector Architectures provide an higher throughput at the expense of more hardware for concurrent processing.

Vector Architectures are very useful for multimedia applications, where data can be processed concurrently, increasing considerably the system throughput.

With the growing popularity of Machine Learning applications, the Graphics Processing Unit (GPU) component has gained popularity with the implementation of hundreds of executing units, enabling the processing of large batches of data concurrently.

#### 2.2.2 Instruction-Level Parallelism

Instruction-Level Parallelism (ILP) is the parallel processing of multiple instructions from a thread of execution and can be implemented at Software and Hardware level [9].

The hardware implementation of ILP is considered Dynamic Parallelism, where the processor selects a set of instructions to be processed in parallel.

The software implementation of ILP is described as Static Parallelism, where the compiler analyze the program code and decide which instructions should be processed in parallel. Modern compilers and processors try to take as much advantage as possible from the ILP, since the majority of the programs are coded in sequential blocks of instructions.

In Computer Architecture the ILP is exploited through the following techniques:

• Pipelining - Instruction execution is partialized, each stage of the pipeline handles a part of the instruction enabling multiple instructions to be processed in parallel;

- Superscalar execution Implementation of multiple execute units, i.e., CPU elements that

process data as coded by the software application, to enable several instructions to be

executed in parallel;

- Out-of-order execution The sequence of the instructions is modified, without violating data dependencies, to enable parallel execution of a block of instructions;

- Speculative execution This technique is used for control flow instructions (e.g. branch),

in which the result is predicted and the respective part of the instruction is executed before

the control flow is computed itself. This method avoids the CPU stall, waiting for the control

flow instruction to be executed, but if the prediction is wrong the CPU has to discard the

current data and start executing the correct instructions from the start [10].

#### 2.2.3 Pipeline

The pipeline implementation yields a reduction in the average execution time per instruction in the computational system. Although the CPU instruction throughput is increased, the execution time of each instruction increases slightly due to overhead in the control of the pipeline and the fact that each instruction must pass by all stages. The increment in the throughput is due to the exploitation of the parallelism among instructions in a sequential instruction stream, as represented in the figure 2.4[11], where each pipeline stage executes different actions of an instruction, enabling multiple instructions to be processed in parallel.

|                     |    |    |    | С   | lock numb | er  |     |     |    |

|---------------------|----|----|----|-----|-----------|-----|-----|-----|----|

| Instruction number  |    | 2  | 3  | 4   | 5         | 6   | 7   | 8   | 9  |

|                     |    |    |    |     |           |     |     |     |    |

| Instruction i       | IF | ID | EX | MEM | WB        |     |     |     |    |

| Instruction $i + 1$ |    | IF | ID | EX  | MEM       | WB  |     |     |    |

| Instruction $i + 2$ |    |    | IF | ID  | EX        | MEM | WB  |     |    |

| Instruction $i + 3$ |    |    |    | IF  | ID        | EX  | MEM | WB  |    |

| Instruction $i + 4$ |    |    |    |     | IF        | ID  | EX  | MEM | WB |

**Figure 2.4:** Simple RISC pipeline designed for a five-cycle instruction executed. The processor performance is increased by five times, compared with a processor not pipelined. The pipeline is defined within the stages: IF = instruction fetch, ID = instruction decode, EX = execution, MEM = memory access, and WB =write-back.

Pipeline designing faces hazards, situations that prevent the next instruction from the instruction stream to be executed in its designated clock cycle, which impacts, negatively, the CPU throughput [11]. The three classes of hazard are:

- Structural hazard: A structural hazard refers to a situation where different instructions require access to the same resource simultaneously. The pipeline stalls the next instruction until the resource is available, delaying the execution of the instruction stream.

- Data hazard: A data hazard occurs when the next instruction to enter the pipeline depends on the result of the computations of the previous instruction. The pipeline stalls the execution of the new instruction until the completion of the current one.

- Control hazard: A control hazard happens when the pipeline misses the branch prediction and consequently pulls instructions that should not be executed. The whole pipeline data has to be discarded and the correct instructions fetched.

Compilers take into account the pipeline implemented by the underlying processor and reorganize the instructions, when necessary and possible, to try to avoid pipeline stalls.

#### 2.2.4 Cache

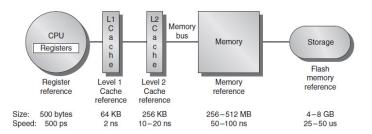

Modern computer memory is implemented through hierarchy levels, represented in figure 2.5[11], to optimize memory access and the overall performance of the computer system. Cache memories, a faster type of memory, are implemented closer to the CPU to enable more efficient data access, by avoiding constant direct fetches from main memory and its inherent high latency.

**Figure 2.5:** Memory hierarchy in modern Computer Systems, targeting a more optimized data access through implementation of faster and smaller memories between the processor and the Main Memory.

The Cache concept is based on the principle of locality, which is defined in computer science as the propensity of a processor to access a set of memory locations repetitively within a period of time. The principle is divided into two types: temporal and spatial locality. The temporal locality states that a block of data is likely to be reused within a short period of time and the spatial locality refers to the reuse of blocks of data close in storage locations [11].

In a computer system, there are two types of cache that can be implemented: Instruction and Data caches.

Instruction cache fetches chunks of instructions from code memory, based on the concept that most programs will execute the instructions sequentially.

Data cache stores frequently used data for future computations, avoiding the costly access to main memory. One popular example is the loop constructs of the programming languages, where the same data is used consecutively.

### 2.3 Data Representation

Data representation in a computational system refers to how data is stored and process within the computer circuitry. In modern computers, there are several data formats available fitting different use cases, such as the floating-point format that targets the representation of real numbers.

### 2.3.1 Floating-Point Representation

In a computer system, the Floating-Point data type is used for the representation of an approximation of a real number. This data type is very used in systems where very small or very large numbers are used and great precision is required.

One popular example is Machine Learning applications, which requires the use of precise coefficients to achieve the desired performance.

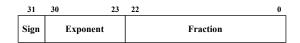

The Institute of Electrical and Electronics Engineers (IEEE) defines two Floating Point formats: Single and Double Precision. The Single Precision standard represents the real value within 32 bits, divided into 23 bits for the Fraction, 8 bits for the exponent and 1 bit sign, as represented in figure 2.6.[12]

**Figure 2.6:** Single Precision Floating Point representation, as defined by the IEEE Standard for Floating-Point Arithmetic.

The Double Precision standard represents the real value within 64 bits, divided into 52 bits for the Fraction, 11 bits for the exponent and 1 bit sign, as represented in figure 2.7.[12]

**Figure 2.7:** Double Precision Floating Point representation as defined by the IEEE Standard for Floating-Point Arithmetic.

The Fraction consists of the significant bits of the number and depending of the notation of the exponent it might be an integer or a fraction. The Fraction section is stored in the Two's Complement by the IEEE Standard for Floating-Point Arithmetic. [12]

The Exponent section stores the coefficient value used to compute the real number and is stored as the excess of 127, for Single Precision, and of 1023, for Double Precision. The calculation of the real number x from Single and Double Precision, respectively, is given by the equation (2.1), where S represents the signal bit, F the Two's Complement Fraction and E the excess exponent.

$$x = (-1)^{S} * (1.F) * 2^{(E-127)}$$

$$x = (-1)^{S} * (1.F) * 2^{(E-1023)}$$

(2.1)

Floating-Point operations within a computer system can not be handled by the same circuitry which processes other data formats. The Floating-Point Unit (FPU) is a co-processor designed for handling Floating-Point data, including addition, subtraction, multiplication and division. Software implementations that rely heavily on Floating-Point computations face performance problems since in a computer there is a limited number of FPU available therefore multiple calls to the FPU will generate a bottleneck on the system.

#### 2.3.2 Fixed-Point Representation

Fixed-point is a representation of real numbers, similar to the floating-point format, but with a constant number of digits before and after the radix point, the separation between the integer part and the fractional part of the real number. This representation is used when the processor does not implement a Floating Point Unit or when it is necessary to accelerate the computation of real numbers.

A Fixed-Point value is simply a real number scaled by a pre-determined factor and truncated to an integer. The scaling factor is recommended to be a power of 2 for computation efficiency or a power of 10 for human convenience.

Addition and Subtraction of two fixed-point values, with the same precision, can be done by simply computing their respective integer arithmetic operation. Multiplication can also be executed through the respective integer operation, but the scaling factor is squared.

The division operation requires the re-scaling of the numerator value, i.e., multiplication of the numerator twice by the scaling factor. After this step, the division can be computed as it would be with integer representation.[13] Fixed-Point representation also presents advantages in terms of hardware development, since the circuit for fixed-point is less complex when compared to floating-point, resulting in smaller chip size and therefore less manufacturing cost. Fixed-Point representation is also simpler to implement in combinational circuits, such as the Arithmetic Logic Unit (ALU).

Another benefit of implementing a component using fixed-point instead of floating-point for real data representation is that fixed-point hardware is more power-efficient.

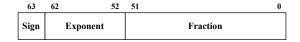

### 2.3.3 Quantization

Quantization is a mathematical process that maps high precision fractional values to smaller integer values. This process is very beneficial in terms of storage and performance, due to faster computation of the integers and better power energy efficiency when compared with floating-point.

The Quantization process has been a subject of great interest in the porting of machine learning models for embedded deployment since these systems often have limited memory and power consumption is a very relevant factor. Machine learning frameworks, like Tensorflow or PyTorch, have popularized the use of 8-bit integers for the implementations of optimized models,

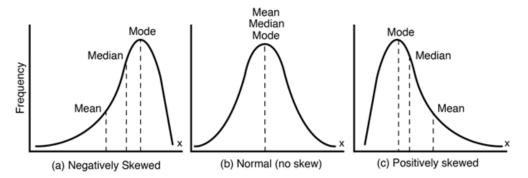

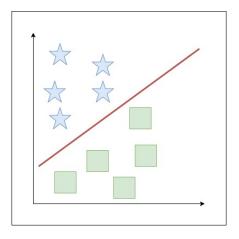

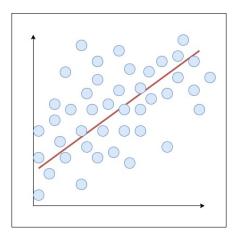

reducing considerably the memory usage and providing faster execution times. The quantization process defines a range of values within the input data that can be mapped, called compression layers. The number of layers is given by  $2^{bitwidth}$ . Each layer multiplied by the scale factor, or most commonly known step size, produces the decompressed value, an approximation of the original value. Quantization is a lossy compression, which means it will introduce an error in computations [14]. Quantization can be of two types: Uniform and Non-Uniform.

In the Uniform Quantization, the compression layers are uniformly spaced, i.e., the step size is constant.

In the Non-Uniform Quantization, the step size has different values for different layers.

Non-Uniform Quantization produces a smaller quantization error but demands more complex computations. The Uniform Quantization, which is used in this dissertation, defines the step size value by using the extreme values of the input data and the desired bitwidth for the representation. The operation is defined in the equation 2.2.

$$\Delta = \frac{max(x) - min(x)}{2^{bitwidth} - 1} , x = [x_0, x_N] \in \mathbb{R}$$

(2.2)

The compression layers are the range of values possible to be represented with the desired bit width and each input value must be mapped to one of those values. The function that transforms an input value into a quantized value is commonly called the kernel, and the Uniform Quantization is defined by 2.3.

$$Q(x) = \lfloor \frac{x}{\Delta} + bias \rfloor \tag{2.3}$$

One well known example of quantization is the Analog-to-Digital Converter (ADC) component, used to convert the voltage applied in the input to integer values. In a system where the voltage sampled by the ADC ranges from 0 to 10 and it is required to be represented the values within a 4-bit bitwidth, the quantizer is composed by 16 compression layers, with a step size of 0.66(6).

The result of the quantization is represented in the graphics of the figure 2.8, where it is visible the loss of precision associated with the quantization error.

**Figure 2.8:** The graphic on the left side shows the voltage applied to and ADC, ranging from OV to 10V. The graphic on the right side shows the quantization results for the different possible values applied to the ADC.

## 2.4 Linux and Embedded Systems

Linux OS began as a homemade project in 1991, developed by a young computer science student at the University of Helsinki named *Linus Benedict Torvalds*, who was a strong admirer of the Unix and smaller Unix-based operating systems. Several programmers contributed to the project through a *mailing list* forum in the early stages of the project and on 5th October of 1991, the first release was announced [15]. Since its first release Linux has been widely adopted between the programming community, for the ease of use and freedom given to the user, as well as the fast software development to support new hardware and the fact that its insertion in the system can be made in a modular way, without having to reboot the system.

Another reason why Linux became so popular is the fact it is distributed under the General Public License (GPL) license [16], which grants the user with the rights to execute, modify and deliver without any cost associated.

With a vast community supporting and constantly updating the Linux OS kernel it has become more robust and reliable and nowadays is present in a wide range of devices and application areas, more than any other OS.

#### 2.4.1 Embedded Linux

Embedded systems have grown from simple bare-metal applications, running in a very resource-limited environment, to supporting OS and all their functionalities [17]. The porting of Linux OS

has been a major factor of why the embedded systems are nowadays present in so many devices [18].

Figure 2.9: Importance of connectivity in modern devices.

The key features that make Linux OS so desirable for embedded systems are:

- Robustness Offers robust features for communication, file management and graphics, making it suitable for critical-mission applications. Linux systems can operate without having to reboot for a prolonged time, even if an application program crashes it will not compromise any system features;

- Portability Applications developed in embedded Linux can be used in different target platforms without any major reworks. This feature enables the re-usage of the systemlevel features for several platforms.

- Ease of customization Easy to configure accordingly to the target system needs. Software to support new hardware can easily be added, as well as other system-level features;

- Ready Support Has a great community that actively contributes with updates and support,

so any developer can get help with existing issues by accessing a Linux User Group forum.

Several industries have been including Linux-based OS in their systems, due to the current demand for increased connectivity and growing popularity of the IoT concept, as represented by the figure 2.9.[19] One well-known example is the automotive infotainment system, present in almost every recent model.[20]

#### 2.4.2 Linux and Memory Management

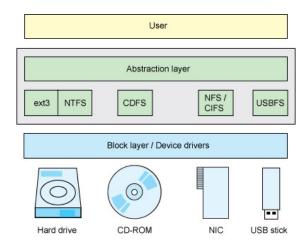

Linux is a Unix-based OS, therefore the key philosophy concerning memory management is "'Everything is a file" [21]. In this concept, every resource and inter-process communication is considered as a stream of data. Each resource is accessible through a filesystem, which differs from device to device. The Virtual Filesystem is a kernel software layer that provides an interface for communication between the user space and the respective filesystem, through system calls [22]. The purpose of this layer is to allow interaction with every resource's uniformly, as illustrated in figure 2.10[22].

Figure 2.10: Layer hierarchy for device access in Linux OS.

Another important implementation detail, concerning memory management in Linux OS, is that a process does not access physical memory directly, instead it operates between a range of virtual addresses, denominated Virtual Address Space, which are allocated by the OS.

The Virtual Address Space starts at a low address, normally 0, and extends to the highest value defined by the system, as well as supported by the physical memory. The Virtual Address Space allocation is advantageous in terms of:

- Memory allocation: The OS is responsible for the memory assignment, reducing the overhead at the start of the process execution, as well as avoiding address collisions between running entities;

- Memory protection: Each process has its own isolated virtual address, preventing access from unauthorized entities;

Memory fragmentation: Virtual memory enables the use of the paging technique, allowing non-contiguous blocks from physical memory to be mapped as a contiguous range of virtual addresses. The paging technique also gives the possibility to the system to allocate more memory than physically available, using a portion of the hard disk as a RAM extension, named Swap Space.

Virtual memory handling, from the translation of the virtual to physical addresses, as well as the implementation of the paging architecture, is performed by the Memory Management Unit (MMU) hardware component.

#### 2.4.3 Linux and Real-Time applications

Linux was designed for a desktop environment, focusing on providing an enjoyable experience to the user on top of a time-sharing preemption concept, where every process is guaranteed to have a minimum of execution time, promoting a high throughput. This scheduling policy differs from the ones used in real-time applications, where the system throughput is not the key factor, instead the focus is set on the priority of the processes, which is the determining factor in the schedule routine for selecting the next entity to run. Although Real-Time concepts are not present in the Linux kernel, there are several active researches to make it suitable for mission-critical systems. The PREEMPT\_RT patch is a popular solution to adapt some features of the kernel, more specifically the preemption mechanism, to Real-Time applications.

For the system to be suitable for Real-Time it is necessary to ensure the system is capable of acknowledging and servicing a critical event within a bounded latency.

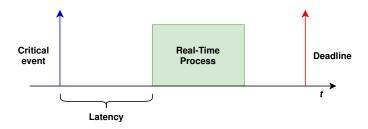

## 2.4.4 Latency

The time difference between the event occurrence and the system response, described in figure 2.11, is denominated Real-Time latency and, as explained in the previous section, is part of the time correctness concept. Real-time latency results from a series of steps the system executes to handle critical events.

Figure 2.11: Real-Time system response to a critical event.

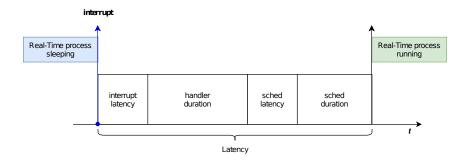

The Real-Time process, implemented as the system response for a critical event, remains in a Sleep state until the preemption is requested. The latency of the system response is composed of the interrupt and the scheduler executions, which are described in detail in image 2.12.[23]

The Interrupt latency is the required time for the system to acknowledge the critical event and trigger the execution of the defined handler. The handler is generally a small routine, designed for fast execution to avoid suspending the normal execution flow longer than required. Before exiting the handler routine a context switch is requested to transfer control to the respective Real-Time process.

The Scheduler latency is the time delay between the context switch request and the scheduler routine to start its execution. The Scheduler component selects the next schedulable entity to transfer control.

Figure 2.12: Detailed Real-Time system's response to a critical event.

#### 2.4.5 Preemption

Preemption is a concept from the OS area which avoids the lock of a CPU core when an entity is waiting on a resource or other entities are required to run.

In Real-Time Systems, preemption enables the interruption of a running process, which is transitioned to a Sleep state, for the critical event response to be executed. A preemptive kernel enables running kernel tasks, i.e., system calls or the abbreviated form syscall, to be interrupted and suspended, avoiding the unpredictability associated with system calls, which can be very time consuming due to their dependability on resource availability.

A preemptive kernel also avoids a system call to crash the system, in case it enters an infinite loop or an unrecoverable state.

Preemptive kernels are highly suitable for systems where device drivers are implemented in the kernel space.

#### 2.4.6 Real-Time Kernel Patch

A patch is a set of changes in the application files or data, used to fix, improve or add new functionalities to the system.

Patching makes it possible to modify a compiled system without access to the source code. This requires a thorough understanding of the object code to avoid the insertion of bugs. The PREEMP\_RT patch was developed for transforming the Linux kernel into a preemptible kernel, eliminating the possibility of a higher priority process to be blocked by a lower priority process running kernel code. A preemptible kernel approximates Linux to an RTOS behavior, making it suitable for Real-Time applications [24]. The PREEMP\_RT patch introduces the following changes to the Linux kernel:

- Kernel locks The Linux kernel implements two types of locking mechanisms: spinlocks

and mutexes. The spinlock entity will try the lock until it is available, while the mutex

causes the process to be transitioned to the Sleep state.

- The PREEMP\_RT patch redefines the spinlock implementation with mutexes, a mutex-like entity that implements the priority inheritance protocol.

- Priority inheritance The Priority Inheritance protocol tries to avoid lower-priority jobs to blocks high-priority ones. This is done by increasing the blocking process's priority to unblock as fast as possible the higher-priority dependent.

This protocol is added to the implementations of semaphores and spinlocks entities;

The drawback of these modifications on the Linux kernel is the increased complexity and latency of the source code. The PREEMP\_RT patch allows the creation of non-preemptible kernel sections through the use of raw\_spinlock\_t. The PREEMP\_RT patch also introduces two new possible configurations for the interruptions services requests, giving the possibility to define them as hard or soft real-time:

- CONFIG\_PREEMPT\_HARDIRQ In this configuration, an ISR is run in process context, which makes it a schedulable entity. This means that an ISR can have an assigned priority, as well as being preempted by higher-priority interrupts.

- CONFIG\_PREEMPT\_SOFTIRQ An ISR is run within the context of the kernel's daemon

ksoftirqd, which is promoted to real-time making it a schedulable entity for the SCHED\_FIFO.

SCHED\_FIFO is a simple scheduling algorithm where a running task can only be preempted by a higher priority entity, otherwise, it will execute until reaching the end of its

execution flow.

Although the real-time patch tries to eliminate most of the unbounded latencies present in the Linux kernel, which dictate a non-deterministic behavior, it still can not be considered a hard Real-Time OSRTOS.

Embedded Linux with the PREEMPT\_RT patch applied is still a great solution for critical systems such as robotics or computer that communicate with hard real-time software.

## 2.5 Image Processing

Image processing is the process of manipulating digital images through an algorithm, altering the original properties of the pixel data. Several systems use image processing algorithms to modify the input image or to process the pixel data to extract relevant information, as is the case of Computer Vision applications.

## 2.5.1 Image Decoding

An image is a very large data structure containing pixel information and the synchronization signals necessary for a playback device to be able to display it.

The Image synchronization signals, are used to synchronize the image dimensions, and consequently the image active area, for the playback device to be able to display correctly.

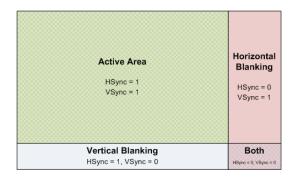

**Figure 2.13:** Image perception by a playback device. The synchronization signals dictate the active are of the image.

The synchronization signals communicate to the playback device through a rising edge, i.e., the signal changes value from 0 to 1, and a falling edge, i.e., the signal changes value from 1 to 0, of the Horizontal Synchronization (HSYNC) and Vertical Synchronization (VSYNC) signals, illustrated in the figure 2.13. [25]

Image processing can be problematic in terms of storage and transmission latency since the acquisition system that samples the surrounding environment transmits the frames to the system's main memory. To avoid high latency values, in the mentioned transmission, images are encoded, targeting a decreased size, and decoded when viewing or editing is requested. Image compression and decompression are handled by a component denominated Codec, which is developed specifically for each image file format. Codec compression can be Lossless or Lossy.

Lossless compression processes the original data while retaining its information, which results in a decoded image with the same quality as the original.

Lossy compression tries to achieve a higher level of compression, reducing the quality of the original image. Consequently, the decompressed image will have decreased quality, compared with the original data. The development of the codec for the desired file format is complex, timewasting and error-prone. Since computer vision is a very popular area in recent years, there are multiple open-source codec solutions for all the different file formats, which can easily be integrated into a user defined application.

#### 2.5.2 Color Space Conversion

In image processing applications it is common to convert images from the original to a specific color space, which better fits the needs of the system. A color space is an abstract model that describes how color is represented, enabling its reproduction through a physical device. The most popular color space is the RGB, which is the default for image processing systems, where color is defined by the 3 channels Red, Green and Blue.

HARVA is an Edge Detection model, where the main concept is based on the theory that object edges have higher intensity values than the background. The RGB color space, usually implemented as default in the Codecs, does not suit this use case so a color space conversion to a more appropriate color model is necessary.