# Essentials of computing systems

João M. Fernandes

Coleção Educação | Ciências, Engenharia e Tecnologia

AUTOR João M. Fernandes

COORDENAÇÃO EDITORIAL Manuela Martins

FOTO CAPA luzvykova laroslava/Shutterstock

PAGINAÇÃO EM LATEX João M. Fernandes

EDIÇÃO UMinho Editora LOCAL DE EDIÇÃO Braga 2022 ISBN 978-989-8974-60-0 DOI https://doi.org/10.21814/uminho.ed.33

Os conteúdos apresentados (textos e imagens) são da exclusiva responsabilidade dos respetivos autores. © Autores / Universidade do Minho – Esta obra encontra-se sob a Licença Internacional Creative Commons Atribuição Compartilha Igual 4.0. UNIVERSIDADE DO MINHO

# Essentials of computing systems

João M. Fernandes

Coleção Educação I Ciências, Engenharia e Tecnologia

### Preface

#### About the book

Computers were originally invented to solve all sort of mathematical problems. Nowadays, computers do much more than that and are present in all human activities. In fact, a computer is a fantastic machine capable of doing the most amazing tasks, if an appropriate program is provided. A computer system contains hardware and systems software that work together to run software applications. Interestingly, the underlying concepts that support the construction of a computer are relatively stable. In fact, (almost) all computer systems have a similar organisation, i.e., their hardware and software components are arranged in hierarchical layers (or levels) and perform similar functions. This book was written for programmers and software engineers who want to comprehend how the components of a computer work and how they affect the correctness and performance of their programs.

i

In fact, understanding how a computer works is a fundamental knowledge for software engineers to comprehend the principles governing the execution of the programs they develop or maintain. It is also a fundamental knowledge if one wants to optimise the performance of a program, to write a compiler, or to develop an embedded system. If a programmer knows exactly how the computer hardware operates, she can write efficient programs. For example, the method used to map main memory to cache can have a huge impact on the order by which array elements are accessed. Therefore, computer scientists and software engineers must understand how computer hardware interacts with software. This is the objective of this book, which is focused on describing the fundamental aspects of computers, by studying their organisation and structure.<sup>1</sup>

This book was originally written to support the courses on Computing Systems at Departamento de Informática, Universidade do Minho. The initial structure of these courses was defined by Alberto J. Proença, with the idea of allowing students to understand the main principles that govern the operation of a computer. This book still follows that idea, but was tuned to focus on the essential elements of computers that software engineers must master. Anyway, we hope that instructors from other universities will adopt this book for their courses.

<sup>&</sup>lt;sup>1</sup> The distinction among these two terms is fuzzy and is out of the scope of this book.

#### PREFACE

This book addresses a very fundamental aspect related to the Computing discipline, so it is expected that any university-level student is able to understand its contents without major problems. Anyway, the reader is supposed to have a relatively good knowledge about how to program a computer in a high-level programming language, like C.

The book is structured in six chapters. Chapter 1 introduces the different levels which one can see a computer, representing each level a distinct abstraction of the computer. This chapter also describes the von Neumann architecture, which is followed by all modern computers. Chapters 2 and 3 address cover the different forms of discrete data found in computers. Chapter 2 introduces the main concepts and techniques related to the representation of textual information, instructions, images, and audio. Chapter 3 explains how numbers are represented in computers. Chapter 4 discusses the details of the IA32 assembly language and it discusses how high-level programs (written in C) get compiled into this form of machine code. Chapter 5 presents the main principles of caches, namely the different mapping functions and replacement algorithms. Chapter 6 explores how to make programs run faster via several different types of program optimisation. Each chapter has a set of exercises to ensure that students put in practice the concepts presented. The book provides answers to almost all those exercises to allow students to check their progress. A glossary, which provides brief definitions of all key terms from the chapters, is also included.

#### About the author

João Miguel Fernandes is full professor on software engineering at the Dep. Informatics, School of Engineering, UMinho.

João holds a 5-year degree in Informatics Engineering (1991), and a master degree in Informatics (1994), both from UMinho (Braga, Portugal). In May 2000, he has completed his Ph.D. thesis in Informatics/Computer Engineering, from UMinho, with a thesis entitled "An object-oriented methodology for embedded systems development."

He has been an invited researcher/professor at Universidade do Algarve (Portugal), University of Bristol (United Kingdom), Aarhus University (Denmark), TUCS (Turku Centre for Computer Science, Turku, Finland), Universitatea Tehnică Gheorghe Asachi (Iași, Romania), UFSC (Universidade Federal de Santa Catarina, Florianópolis, Brazil), ISCTEM (Mozambique), and ISTM (Angola).

João is the main author of the book "Requirements in engineering projects" (Springer, 2016) and co-editor of the book "Behavioral modeling for embedded systems and technologies: Applications for design and implementation" (IGI Global, 2009). He is the author of more than 130 scientific publications with peer revision on international conferences, journals and chapters of books. His publications have collected more than 2.000 citations. He is member of the Editorial Review Board of the Journal of Information Technology Research (IGI Publishing) and editor of Open Computer Science (De Gruyter/Springer). Additionally, he has already served as a scientific reviewer for an Addison-Wesley book, for scientific journals and for many symposia. He also regularly serves as a member of the Programme Committees of international conferences and workshops. He has been involved in the organization of various international scientific events, including the 3rd Int. Conf. on Application of Concurrency to System Design (ACSD 2003), the 5th IFIP Int. Conf. on Distributed and Parallel Embedded Systems (DIPES 2006), the 3rd International Summer School on Generative and Transformational Techniques in Software Engineering (GTTSE 2009), the 31st International Conference on Application and Theory of Petri Nets and Other Models of Concurrency (PETRI NETS 2010), the 10th International Conference on Application of Concurrency to System Design (ACSD 2010), the 6th International Conference on Software Business (ICSOB 2015), and the Model-based Methodologies for Pervasive and Embedded Software (MOMPES) workshop series.

João conducts his research activities in Software Engineering, with a special interest in the following topics: software modeling, requirements engineering, embedded software, software process, bibliometrics. Within his research and teaching activities, he maintains regular collaborations with the industry. iFlow, a research project developed in cooperation with Bosch Portugal, received the 2016 Annual Logistics Excellence Award (PEL 2016) from the Portuguese Logistics Association (APLOG).

#### Acknowledgments

A number of colleagues have read the intermediate versions of the book and provided useful suggestions. In particular, I would like to thank Alberto Proença, Luís P. Santos, and Manuel Alves. I would also like to acknowledge Luís Gomes and João M.P. Cardoso, who acted as reviewers and gave useful feedback and many good suggestions, to ensure a quality textbook. The publishing team at UMinho Editora has been wonderful to work with and a special thanks goes to Carla Marques for the constant help and support. Alberto Simões and Bruno Dias helped me in adjusting the  $\&T_EX$  styles to comply with the formats of the publisher. Lastly, and most importantly, I am deeply indebted to my wife Raquel and our two children Gonçalo and Constança. This book would not have been written without their patience and encouragement.

## Table of Contents

| Pre | face .                                                      |                                                                                                                                                                                                                                 | i                                                              |

|-----|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1   | 1.1<br>1.2<br>1.3                                           |                                                                                                                                                                                                                                 | 1<br>4<br>5<br>7<br>8<br>9<br>10<br>13                         |

| 2   | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                      | Digital abstraction .<br>Bits, bytes and words .<br>Textual information .<br>Machine-level instructions .<br>Images .<br>Audio                                                                                                  | 15<br>16<br>18<br>20<br>21<br>22<br>23                         |

| 3   | <b>Rep</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.5<br>3.6 | Positional numeral systemsOctal and hexadecimal numbersConversions between different basesNegative numbers3.4.1 Sign-magnitude3.4.2 One's-complement3.4.3 Two's-complement3.4.4 Excess representationsTwo's-complement addition | 25<br>25<br>27<br>29<br>30<br>31<br>31<br>32<br>33<br>34<br>36 |

#### TABLE OF CONTENTS

|      |                                                                       |                                                                                         | codes for c                                                                                                                                                    |                                                                                          |                                  |                        |                      |                 |                                       |               |      |                                       | 41<br>42                                                 |

|------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------|------------------------|----------------------|-----------------|---------------------------------------|---------------|------|---------------------------------------|----------------------------------------------------------|

| 4    | 4.1<br>4.2                                                            | Compi<br>IA32 a<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6<br>4.2.7<br>4.2.8 | <b>tion-set an</b><br>lation of C<br>ssembly lar<br>Registers<br>Data types<br>Operands<br>Data move<br>Arithmetic<br>Control ins<br>Procedures<br>Data struct | code to a<br>nguage<br>ment ins<br>and logi<br>structions<br>s<br>tures                  | struction<br>ical inst           | y code                 |                      |                 |                                       |               |      | · · · · · · · · · · · · · · · · · · · | 47<br>49<br>50<br>51<br>52<br>55<br>59<br>63<br>68<br>71 |

| 5    | 5.1<br>5.2<br>5.3                                                     | Main p<br>Mappi<br>Replac                                                               | <b>ory</b><br>orinciples<br>ng function<br>cement algo                                                                                                         | orithm                                                                                   |                                  | · · · · · · · · ·      | <br>                 | <br>            |                                       | · · · · · · · | •••• | <br>                                  | 75<br>75<br>78<br>82<br>82                               |

| 6    | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul> | Main p<br>Limita<br>Machi<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>Machi<br>Cache         | isations<br>principles<br>tions of the<br>ne-indepen<br>Code moti<br>Eliminatio<br>Loop unro<br>Reduction<br>ne-depende<br>oriented op                         | compile<br>dent opti<br>on<br>n of unne<br>lling<br>of the nu<br>ent optim<br>otimisatio | ecessary<br>umber o<br>nisations | y access<br>of process | ses to n<br>edure ca | nemory          | · · · · · · · · · · · · · · · · · · · |               |      | · · · · · · · · · · · · · · · · · · · | 85<br>86<br>88<br>90<br>91<br>93<br>95<br>95             |

| Solu | tions                                                                 | to exe                                                                                  | rcises                                                                                                                                                         | •••••                                                                                    |                                  |                        |                      |                 | •••••                                 |               | •••• |                                       | 99                                                       |

| Glos | sary                                                                  |                                                                                         |                                                                                                                                                                | •••••                                                                                    |                                  | •••••                  | • • • • • • • •      | • • • • • • • • | •••••                                 |               | •••• | • • • • •                             | 101                                                      |

| Refe | renc                                                                  | es                                                                                      |                                                                                                                                                                | •••••                                                                                    |                                  |                        |                      |                 | •••••                                 |               | •••• |                                       | 111                                                      |

| Inde | x                                                                     |                                                                                         |                                                                                                                                                                |                                                                                          |                                  |                        |                      |                 |                                       |               |      |                                       | 113                                                      |

## Chapter 1 Computer systems

**Abstract** This chapter introduces the different levels at which one can see a computer. Each level represents a distinct abstraction of the computer. This division in layers permits those that work at a given level to be unaware of what happens in the other levels. This perspective allows unnecessary details to be omitted, which reduces complexity. This chapter also describe the von Neumann architecture, which is followed by all modern computers. It includes a CPU, the main memory, and some input/output devices.

#### 1.1 Levels of a computer

A **computer** is a programmable device that can automatically execute a sequence of instructions on data once programmed for the task. It can store, retrieve, and process data according to the instructions. The sequence of instructions that describe the task to be performed is the **program**.

It is relevant here to distinguish a computer from a calculator. A device is considered as a computer if it has both of the following characteristics, and is a calculator if it lacks either or both (Fenwick, 2015, pp. 12–13):

- Data-dependent instruction sequence. A computer must include conditional branch constructors (like IF-THEN-ELSE, SWITCH, and DO-WHILE), whose execution depends on values that can only be calculated during the program execution (i.e., values that are not known while programming).

- **Data-dependent data selection**. A computer must be able to use data to determine the actual data to be used in calculations. This mechanism is used, for example, when accessing arrays and other types of structured variables.

The electronic circuits of each computer are able to directly execute a limited set of simple instructions, into which all its programs must be converted before they can be executed. These simple instructions are operations like:

- add two numbers;

- test if a number is equal to zero;

- copy a piece of data from one part to another;

- decide what instruction to execute next based on the evaluation of some logical condition.

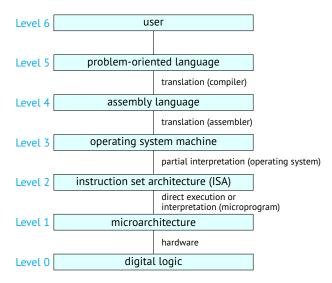

These primitive instructions constitute a language, called a machine language, that programmers can use to operate the computer. The engineers that design a computer must decide what instructions to include in its machine language. Programming with machine languages is usually difficult, error-prone, and tedious for people, because they tend to be simple and cryptic. The machine language exists mainly to be executed by the computer and not necessarily to be understood by humans. Even a simple program may require many instructions, which make the program long and consequently hard to master. Fortunately, new languages can be constructed on top of the machine language to rise the abstraction level. This hierarchical approach is recursive, so computer systems can be designed in an organised, structured, and layered way. In general, a computer can be seen as a set of layers or levels, as shown in Fig. 1.1.

Fig. 1.1 A seven-level computer. The support method for each level and the supporting program is indicated below it.

Level 6, the user level, is what everyone who interacts with computers is familiar with. This level contains software applications, like text editors, web browsers, graphics programs, and games. The user at this level sees software applications that he can select to run for specific purposes. He can open a word editor to write a letter, a web browser to access a given website, or a game to have fun. Fortunately, the user can manipulate all these applications at this level, without having any idea on how the lower levels work.

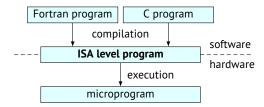

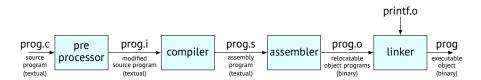

Level 5, the problem-oriented language level, consists of languages, like C, C++, Java, Perl, Python, and PHP, which are appropriate to develop software applications. Such languages are called high-level languages. Programs written in these languages are generally

translated to levels 4 or 3 by translators, known as compilers, or interpreted. For example, Java programs are usually first translated to an ISA-like language, called Java byte code, which is later interpreted. In some cases, level 5 consists of an interpreter for a specific application domain. This level provides data and operations for solving problems in this domain, in terms that people familiar with the domain easily understand.

Level 4, the assembly language level, is really a symbolic form for one of the underlying languages. This level provides a method for humans to write programs for levels 3 and 2 in a form that is not as unpleasant as the virtual machine languages themselves. Programs in assembly language are first translated to level 3 or 2 language and then interpreted by the appropriate virtual or actual machine. The program that performs the translation is called an assembler.

Level 3 is usually a hybrid level. Most of the instructions in its language are also in level 2. This is totally admissible as an instruction at one level can also be present at other levels as well. Additionally, there is a set of new instructions, a different memory organisation, the ability to run two or more programs concurrently, and other features. The new facilities added at level 3 are carried out by an interpreter running at level 2, which is usually called as an **operating system**. The level 3 instructions that are identical to those on level 2 are executed directly by the microprogram (or hardwired control), not by the operating system. In other words, some of the level 3 instructions are interpreted by the operating system and some are interpreted directly by the microprogram. This justifies why this level is classified as hybrid.

Level 2 is the ISA (instruction set architecture) level. Every computer is accompanied by an instruction set manual that describes a strictly numerical language, the so-called machine language. A program at this level is machine code, which means that its instructions can be carried out interpretively by the microprogram or the hardware execution circuits. It is the lowest level representation of a program.

Level 1 is the microarchitecture level, where one sees a relatively small collection of registers, which forms a local memory, and an ALU (arithmetic logic unit), which can execute simple arithmetic operations. The registers and the ALU are interconnected to form a data path, through which the data flow. The basic operation of the data path consists of selecting one or two registers, having the ALU operate on them (e.g., adding them together), and storing the result back in some register.

The operation of the data path is usually controlled by a program called a **microprogram**. On machines with software control of the data path, the microprogram is an interpreter for the level 2 instructions. It fetches, examines, and executes instructions one after the other, using the data path to do so. For example, a SUB instruction is fetched from memory, its operands located and transferred to the registers, the subtraction computed by the ALU, and finally the result transferred to the destination. On a machine with hardwired control of the data path, similar steps are taken, but without an explicit stored program to control the interpretation of the level 2 instructions.

Finally, level 0, the digital logic level, represents the computer hardware. Its circuits execute the machine-language programs of level 1. Level 0 is composed of logic gates and wires. A gate is built from analog components, like transistors. A gate can be viewed as a digital device with a set of inputs that outputs some simple function, like logical AND or OR, of these inputs. This level also includes flip-flops, which are 1-bit memories that can

be used to store a bit (either a '0' or a '1'). A register can be assembled with, for example, 32 1-bit memories, which can be used to hold a 32-bit number.

A fundamental frontier exists between levels 4 and 3. The lowest three levels are intended primarily for running the interpreters and translators needed to support the highest levels. These interpreters/translators are developed by systems programmers, who are specialised in constructing new virtual machines. Levels 4 and above are intended for the applications programmer with a given problem to solve in a specific domain. Another change that occurs at level 4 is the method by which the higher levels are supported. Levels 2 and 3 are always interpreted. Levels 4, 5, and above are usually supported by translation/compilation. Another difference between levels 1 to 3 and levels 4, 5, and higher is the nature of the language provided. The machine languages of levels 1, 2, and 3 are numeric. Programs in these levels consist of long series of numbers (bits), which are appropriate for machines, but very hard for humans. At level 4 and above, the languages contain words and mnemonics that humans are able to easily understand.

To summarise, computers are designed as a series of levels, each one built on its predecessors. Each level represents a distinct abstraction of the computer, with different concepts, objects and operations. This division in layers is very convenient as it permits those that work with the computer at a given level to be unaware, if they wish, of what happens in the other levels. For example, a programmer that works with a level-5 language may not be aware of the principles and mechanisms that permit his programs to be translated to a level-4 language. By analysing or operating computers with this perspective, unnecessary details can be omitted, which reduces complexity.

From a programmer's perspective, it is relevant to understand how computers work at the lower levels. For most cases, knowing what happens in the underlying levels is not mandatory. However, when for example a program written in a high-level language does not execute as expected, is not running as fast as intended, or consumes too much energy, it is often necessary to analyse what is happening at the lower levels. This analysis is only possible if the programmers comprehend how computers operate at those levels.

#### 1.2 Organization of a computer

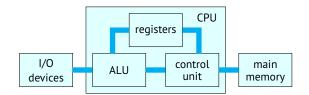

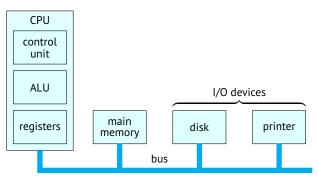

A computer is a complex system that contains millions of elementary electronic components. To abstractly describe a computer, it is essential to follow an hierarchical approach. Almost all uniprocessor (or scalar) computers follow the so-called von Neumann architecture, which includes a CPU, the main memory, and some input/output devices, as shown in Fig. 1.2. The existence of two separate components, one for processing the data and a different one to store them, is a distinguished characteristics of this architecture. All transfers of information between these two units go through the unique channel connecting them, which constitutes a serious bottleneck. This architecture also introduces the stored program concept that makes computers to be general-purpose machines. This section introduces the major components of the computer and the way they are interconnected.

The von Neumann architecture has been extended in several ways to address some of its limitations. A well-known proposal, as illustrated in Fig. 1.3, is the inclusion of a system bus

Fig. 1.2 The von Neumann architecture.

that connects the components of the computer. The system bus has three main elements: data bus, address bus, and control bus. The data bus moves data from main memory to the CPU registers (and vice versa). The address bus holds the address of the data that the data bus is currently accessing. The control bus carries the necessary control signals that specify how the information transfer is to take place.

Fig. 1.3 The system bus model.

#### 1.2.1 Central processing unit

The **central processing unit (CPU)**, also called processor, is the "brain" of the computer. On the machine language level, the operation of the CPU is quite straightforward. It is responsible for the execution of the program, stored as a sequence of machine language instructions in the main memory. Each instruction directs the CPU to perform some basic task, like subtracting two numbers or moving data from one register to another one. The CPU does all this mechanically, without understanding what is the purpose for executing the instruction. This means that the program must be complete and have no errors, since the CPU can only execute it.

The CPU is composed of three major components: control unit, ALU, and registers. The components are connected by a **bus**, which is a collection of electric wires for conducting address, data, and control signals. Buses allow the parallel movement of bits. At a given

moment in time, only one device may use the bus. Buses can be external to the CPU, connecting it to memory and input/output (I/O) devices, but also internal to connect its parts.

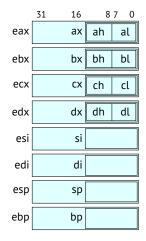

The CPU contains a small number of high-speed memory registers. A **register** is used to store temporary results (like a number) and status information. All the registers have usually the same size, that is, an equal number of bits. Registers can be read and written at a very high speed since they are internal to the CPU. A relevant register is the **instruction pointer** (IP), also known as program counter (PC), which indicates the address of the next instruction to be executed. Another important register is the **instruction register** (IR), which stores the instruction, codified according to the machine convention, currently being executed. Most computers have other registers as well, some of them general-purpose and others for specific purposes.

The arithmetic logic unit (ALU) performs basic operations such as addition, subtractions, and comparisons, which are necessary to execute the instructions. Usually, an ALU has two data inputs and one data output. The operations carried on by the ALU affect the status registers, which indicate attributes related to the last arithmetic or logic operation (e.g., if the result was negative or not). The operation that the ALU must perform is signalised by the control unit, based on the instruction that is executed in each instant.

The **control unit** is responsible for orchestrating the components of the computer to ensure that the instruction that is being executed in each moment produces its exact and expected effects. This is accomplished by activating in the right sequence the control signals that are sent to the computer components. From a conceptual point of view, the execution of an instruction by the CPU can be divided into the following steps:

- 1. Fetch the instruction from memory and store it into the IR.

- 2. Determine the type of instruction.

- 3. If a word in memory is used by the instruction, determine its location.

- 4. If needed, transfer the word from the memory into a CPU register.

- 5. Produce the effects of the instruction, i.e., perform some simple operation dictated by the instruction.

- 6. Change the IP to refer to the next instruction.

This process, called the **fetch-decode-execute cycle**, is repeated indefinitely, from the time that power is applied to the computer, until it is powered off. The CPU receives an instruction from the memory, decodes it, and executes it using data obtained from the memory or already available in the registers. Once the processor finishes the execution of an instruction, it starts the cycle again for the next instruction in the memory, except when a branch instruction was just executed. This cycle is a central concept to the operation of digital computers, since essentially they all just execute instructions, one after the other. The control unit can be seen as a program (a microprogram that can be implemented in hardware) that goes through the set of steps to execute the instructions of another program (i.e., the one that is being executed by the processor).

Most computer systems have a **clock** signal that acts like a heartbeat. The clock signals the passage of time within the computer. A clock emits periodically a pulse, i.e., it transmits a precise pulse with regular intervals of high and low values. The time between two consecutive ticks is called a clock cycle (or clock period), which represents one discrete time unit. The different operations performed by a processor, such as fetching an instruction or decoding it, are synchronised by the clock. All these operations begin with the pulse of the

clock. Therefore, the speed at which the instructions are executed by the processor depends on the frequency of the clock, measured in cycles per second or Hertz (Hz).

#### 1.2.2 Main memory

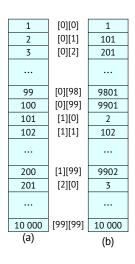

The **main memory** is the component of the computers, where programs and data are both stored. A memory consists of a number of cells or locations, each of which can store a piece of information. Each cell has a number, called its **address**, by which programs can refer to it. A memory with n cells uses addresses from 0 to n - 1. All memory cells have the same number of bits.

The main memory is a random access memory (RAM), which stores a piece of data at a unique address and can recall the data upon presentation of the complete unique address. This is an important aspect, since microprocessors access the memory to fetch instructions and to read or write data in consecutive clock cycles. The addresses of these instructions and data need not be somehow related in a discernible way. In fact, RAM is able to handle random, or more precisely arbitrary, access, that is, any datum can be retrieved as quickly as any other, without favouring any particular location. RAM memories are volatile, which means that the information disappears if the supply voltage is turned off. In contrast, the contents of nonvolatile memory is preserved even after power is removed. For example, the flash memory used in digital cameras is nonvolatile, since the data is not lost when the power is turned off. Physically, the main memory consists of a collection of dynamic random access memory (DRAM) chips.

The **cell** is the smallest addressable unit. Almost all modern computers use 8-bit (1 byte) cells. Bytes are grouped into words. A computer with a 32-bit word has 4 bytes/word, while a computer with a 64-bit word has 8 bytes/word. The word is also important since most instructions operate on entire words, for example, adding two words together. Thus, a 32-bit machine has 32-bit registers and instructions for manipulating 32-bit words.

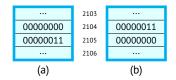

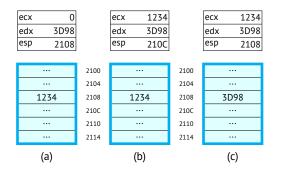

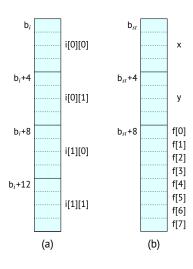

An issue that needs to be handled, when storing a multibyte value in a byte-addressable memory, is the order of the individual bytes. For example, the number 11 0000 0000<sub>2</sub> (represented in base two as explained in Chapter 3) requires two bytes of memory, one storing the low set of eight bits 0000 0000<sub>2</sub> and another one storing the high set of eight bits 0000 0000<sub>2</sub> and another one storied in the memory at location 2104, there are two popular ordering alternatives as shown in Fig. 1.4.

Fig. 1.4 Byte ordering for multibyte: (a) Little-endian, (b) Big-endian.

If the low order byte of a multibyte value is put first in memory (i.e, has the lowest addresses), **little endian** is the adopted alternative. Otherwise, if the high order bytes comes first, **big endian** is the selected order. In both cases, the two-byte number has address 2104, but occupies also the memory cell with address 2105.

Digital computers possess a great versatility. They are machines with finite hardware that can execute whatever programs their users wish.<sup>1</sup> This outstanding flexibility is related to the ability of a computer to load the programs in its internal memory. So, instructions and data are both stored in the memory. By changing the program in the memory, one changes the problem the computer is solving. This justifies the notion of a **stored program computer** (or general-purpose computer), one that can be used for any problem.<sup>2</sup> Additionally, during a computation, a given instruction may also be modified, i.e., changed to a different instruction, a characteristic that is not usually explored. This gives rise to **self-modifying code**, a concept that is particularly straightforward to perform at the machine-level, by directly writing new instructions over the existing ones in the memory. The stored program concept is a fundamental element of many computer models, namely the universal Turing machine and the von Neumann machine. The **Turing machine**, a mathematical model of a simple computer, can be used mainly to analyse the logical foundations of computer systems.

#### 1.2.3 Secondary memory

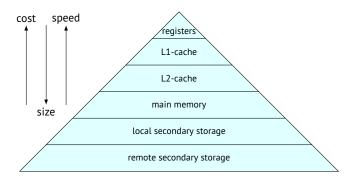

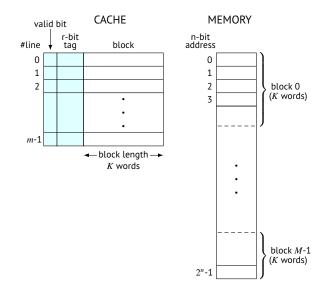

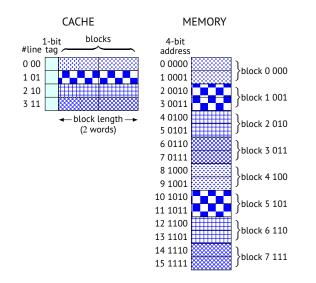

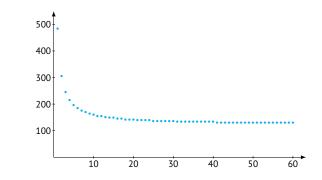

The main memory of a computer is never enough, because people always need to store more information than it can hold. The traditional solution to store a great quantity of data is to use a memory hierarchy, as illustrated in Fig. 1.5. The top level includes the CPU registers, which constitute the fastest memories of the computer. Next come one or more cache memories, which according to Table 1.5, are on the order of 32 KiB to a few megabytes. Main memory is the next level, with sizes ranging from 1 GiB for low-end systems to hundreds of gibibytes for high-end ones. Afterwards, come local secondary storage, which include local disks, magnetic tape and optical disks for archival storage. The final level is remote secondary storage, which includes disks on remote servers that can be accessed over a network.

The overall goal of this hierarchy is to establish a memory system with cost almost as low as the cheapest level and speed almost as fast as the fastest level. All the data in a given level can be found in the next lower level. Each level in this hierarchy is smaller, faster and more expensive per bit than the lower ones. In fact, three parameters increase as the hierarchy is visited from the top to the bottom, as shown in Fig. 1.5 and in Table 1.1.

Firstly, the access time gets bigger. CPU registers can be accessed in a nanosecond or less. Cache memories use static random access memory (SRAM) technology and take a small multiple of CPU registers. Main memory accesses are typically 10 nanoseconds. The biggest

<sup>&</sup>lt;sup>1</sup> Early computers had fixed programs. To modify the program, one was supposed to re-wire and re-structure the machine, which was very tedious and error-prone.

<sup>&</sup>lt;sup>2</sup> There are problems that computers cannot solve. An interesting discussion about the limits of computers is presented by Harel (2000).

Fig. 1.5 A six-level memory hierarchy; Adapted from Bryant and O'Hallaron (2016).

| level              | 1              | 2           | 3           | 4             |

|--------------------|----------------|-------------|-------------|---------------|

| name               | registers      | cache       | main memory | disk storage  |

| typical size       | < 1KB          | < 16 MB     | < 512 GB    | > 1 TB        |

| implementation     | CMOS           | SRAM        | DRAM        | magnetic disk |

| access time (ns)   | 0.25-0.5       | 0.5-25      | 50-250      | 5,000,000     |

| bandwidth (MB/sec) | 50,000-500,000 | 5000-20,000 | 2500-10,000 | 50-500        |

**Table 1.1** Typical levels in the memory hierarchy of a desktop computer; Adapted from Hennessy and Patterson (2007, p. C-3).

gap occurs in the interface between the main memory and the disk, as disk access times are at least 10 times slower for solid-state disks (and much slower for magnetic disks). Tape and optical disk access can be measured in seconds if the media have to be fetched and inserted into a drive.

Secondly, the storage capacity also increases. CPU registers are good for a small number of bytes. IA32, whose instruction set is described in detail in Chapter 4, has eight 4-byte generic registers, i.e., 32 bytes. Caches, which are presented and discussed in detail in Chapter 5, can store tens of megabytes, while main memories a few gigabytes. Solid-state disks have space for hundreds of gigabytes, and magnetic disks for terabytes. Tapes and optical disks are usually kept off-line, so their capacity depends mainly on the owner's budget.

Thirdly, the number of bits that one gets per dollar (or euro) increases down the hierarchy. Programmers need to understand the memory hierarchy, because it has a big impact on the performance of the software programs. The more distant the data is to the CPU, the longer it takes to access it.

#### 1.2.4 I/O devices

Computers are built so that they can be expanded with new I/O (input/output) devices, such as a hard disk, a keyboard, a mouse, a monitor, a printer, an audio output device, a network interface, a scanner. An I/O device is a hardware system used by humans or systems

to communicate with a computer. The CPU must communicate with and control all these devices. So, for each device in a system, there is a **device driver**, which consists of software that the CPU executes when it has to deal with that device. A new device can be installed by connecting the device into the computer and installing its device driver software. The device driver allows the CPU to communicate with the respective device.

As Fig. 1.2 shows, the I/O devices are connected to the computer through busses, which carry data, addresses, and control signals. An address directs the data to a specific device and probably to a particular element within that device. Control signals are used, for example, by a device to alert the CPU that data is available on the data bus.

When a given device produces data that needs to be processed, somehow the CPU needs to take some action. A simple solution, which is not very satisfactory, is for the CPU to keep checking for incoming data over and over. Whenever it detects that data was made available by the device, it processes it. This method is designated as **polling**, since the CPU repeatedly checks the input device to see whether it has any data. Polling is very simple, but is also very inefficient.

To avoid this inefficiency, interrupts are generally used instead of polling. An **interrupt** is a signal sent by a device to the CPU to request its attention. The CPU reacts by suspending what it is doing to answer to the interrupt. For this purpose, the CPU saves information about what it is currently doing so that it can return to it afterwards. This information consists of the contents of important internal registers such as the instruction pointer. Then the CPU jumps to some fixed memory location and begins executing the instructions stored there. Those instructions correspond to the interrupt handler that does the processing necessary to respond to the interrupt. This interrupt handler is a part of the device driver for the device that issued the interrupt. Once the interrupt is processed, the CPU returns to the process that was suspended. To this end, it restores its previously saved state. For example, whenever a key is pressed on the keyboard, an interrupt signal is sent to the CPU. The CPU responds by suspending what it is doing, reading the key that was pressed, processing it, and then returning to the task it was performing just before the key was pressed.

#### 1.3 Instruction-level parallelism

Improving the characteristics of computers, like performance, cost, reliability, energy consumption, is a concern for computer engineers and architects, as they aim to construct the most efficient machines for the users. Performance is an inescapable issue, since making computers run faster is always relevant. One possible approach is to exploit parallelism, which can have different forms: instruction-level, data-level, and processor-level parallelism. This section discusses instruction-level parallelism with pipelining, which explores individual instructions to obtain higher throughput (i.e., more instructions per time unit).

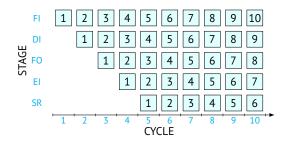

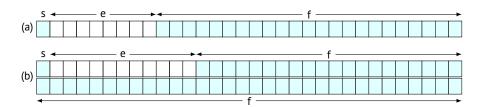

With **pipelining**, the process of executing instructions is divided in stages, allowing multiple instructions to be overlapped in execution. Each stage is responsible for a part of the process and all can run in parallel, thus speeding up the process. Fig. 1.6 shows a possible five-stage pipeline. Stage 1 (FI) is responsible for fetching the instruction from the memory and to place it in the IR. Stage 2 (DI) decodes the instruction, to identify its type and what operands are needed. Stage 3 (FO) fetches the operands, either from registers or from the memory. Stage 4 (EI) carries out the instruction. Stage 5 (SR) writes the result back to the proper destination.

**Fig. 1.6** A 5-stage pipeline.

Fig. 1.7 illustrates the ideal operation of the pipeline. During the first clock cycle, stage 1 handles instruction 1, fetching it from memory. During cycle 2, stage 2 decodes instruction 1 and stage 1 fetches instruction 2. During cycle 3, stage 3 fetches the operands for instruction 1, stage 2 decodes instruction 2, and stage 1 fetches the third instruction. And so on. Thus, during the fifth cycle, stage 5 stores the result of instruction 1, while the other stages are operating on the subsequent instructions.

Fig. 1.7 An ideal five-stage pipeline in action.

The different stages operate in parallel, which permits this process to be accelerated. Pipelining increases the number of instructions that are simultaneously under execution. In fact, instruction **throughput**, which measures the number of instructions completed per time unit, is improved. This improvement occurs without the need to reduce the time that is required to complete each individual instruction, called the **latency**.

With a pipeline, all instructions must pass through each stage. If an instruction has no operand, it could skip stage 3, but to simplify the hardware and the timing, each instruction proceeds through all stages, even if not necessary. As Fig. 1.7 shows, in 10 cycles, six instructions are fully executed. In fact, with this 5-stage solution, after the pipeline is full, one instruction can be potentially executed at each clock cycle, i.e., the throughput is one clock cycle. This rate can be observed from cycles 5 to 10, in which six instructions are completed. Theoretically, if all stages take the same time, then there is a speed up of five, as one individual instruction has a latency equal to five cycles. In fact, the maximum speedup is equal to the number of stages.

The maximum theoretical speed up is however very unlikely to occur in practice, because it is difficult to balance the time it takes to complete each stage. All stages must be equally balanced, otherwise the faster stages must wait for the slower ones. Additionally, the following three major aspects also negatively affect the theoretical speed up:

- 1. resource conflicts,

- 2. data dependencies,

- 3. conditional branch statements.

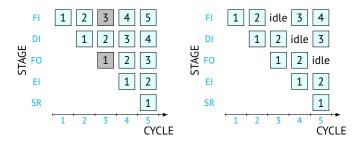

A resource conflict greatly affects instruction-level parallelism. This type of conflict occurs whenever two pipeline stages need to simultaneously access the same resource (e.g., memory). For example, a conflict exists when a given stage is storing a value to the memory, while another one is fetching the instruction from memory. Fig. 1.8(a) shows this situation, because both the instruction fetch (FI) for instruction 3 and the operand fetch (FO) for instruction 1 need a simultaneous access to the memory. This conflict is usually resolved by permitting the operand fetch to occur, while waiting for the instruction fetch, as illustrated in Fig. 1.8(b). Certain conflicts can also be tackled by providing two separate pathways: one for data coming from memory and another for instructions coming from memory.

**Fig. 1.8** A resource conflict in a 5-stage pipeline.

A data dependency occurs whenever the result of one instruction, not yet available, is also the operand of a subsequent instruction. There are some solutions to handle these conflicts. Special hardware can be incorporated to detect instructions whose source operands are destinations for instructions further up the pipeline. By inserting a delay (e.g., a nop instruction that does nothing) into the pipeline, sufficient time passes and the conflict disappears. Some architectures assume that this problem is solved by the compiler, which must reorder instructions, so that there is a delay in loading any conflicting data, but no effect on the program overall behaviour.

Problems in the pipeline can also be caused by a **branch instruction** that modifies the normal execution flow of a program. If the conditional branch is taken, the subsequent instructions must not be executed and the pipeline must be emptied. Some architectures predict the outcome of a conditional branch to try to identify the instructions that will be executed next. In some cases, compilers try to solve branching issues by rearranging the machine code to cause a delayed branch. An attempt is made to reorder and insert useful instructions, but, if not possible, nop instructions are inserted to keep the pipeline full.

12

Another alternative is to initiate fetches on both paths of the branch. When the branch is actually executed, the correct path is identified and the pipeline can be safely continued.

#### Exercises

**Exerc. 1.1**: Describe the following terms with your own words: (a) Compiler; (b) Interpreter; (c) Virtual machine.

**Exerc. 1.2**: Write a small program in a given programming language. Compile it and try to calculate the ratio of source code statements to the machine language instructions generated by the compilation process. Add different types of statements to the high-level program, one at a time, and check how the machine language program is affected.

**Exerc. 1.3**: On a big-endian computer, a 32-bit integer with value 00010010 00110100 01010110 01111000 is about to be stored in the memory at location 132,104. Indicate which memory cells are affected and which values are stored in each one.

**Exerc. 1.4**: Consider that part of the memory of a little-endian computer contains the values shown in the figure. Indicate the value of a 32-bit integer if it is read from the memory location 4365.

| 4362 | 0100 0011 |

|------|-----------|

| 4363 | 0111 0000 |

| 4364 | 0000 0011 |

| 4365 | 0001 0010 |

| 4366 | 1111 1111 |

| 4367 | 0000 0000 |

| 4368 | 0000 1111 |

|      |           |

**Exerc. 1.5**: In a stored-program computer, both the instructions and the data of a program are located in the main memory while it is executed. What are the possible implications if a program accidentally modifies the value that is stored in a memory cell that is related to an instruction?

**Exerc. 1.6**: In a factory, the production process of a given product goes through four steps: preparation, assembly, testing, and packaging. Those steps take the following times, in seconds, to be executed: preparation (20), assembly (30), testing (35), and packaging (35). Calculate the time needed to produce 1000 replica of the product by: **(a)** one single person; **(b)** four persons working in a pipeline.

#### **Further reading**

The history of computers is a very valuable source for better understanding many issues related to computers. Ceruzzi (1998) provides an excellent overview of the history of com-puting in the period 1945-2001. Another interesting material is available in the book edited by Rojas and Hashagen (2000), which includes detailed descriptions about the architectures of the first computers ever built.

The interested reader on issues related to computer organisation and design have several reference books to detail the material presented here. The authoritative book authored by Patterson and Hennessy (2014) deserves a special attention. A good source is the book by Bryant and O'Hallaron (2016), because it describes the concepts underlying all computer systems, but with a programmer's perspective. The book is focused on helping programmers to profit from their knowledge of a computer system to write better programs. Stallings (2019) also provide a very authoritative presentation of computer organisation and architecture.

A very detailed description of different types of secondary memory is presented by Tanenbaum and Austin (2013, Chapter 2). Another important reference for memory systems is provided by Jacob et al. (2008).

## Chapter 2 Representation of information

**Abstract** The different forms of data found in computers may be grouped in three general categories: (1) the numbers used in arithmetic calculations, (2) the letters of the alphabet that are combined to form words in the writing systems of the languages, and (3) other types of discrete symbols that humans use for different purposes. All computers represent these types of data in binary-coded formats, i.e., with bits. Despite this fact, whenever the computer information is presented to humans, it must be transformed into numbers, letters of the alphabet or other symbols. This chapter introduces the main concepts and techniques related to the representation of information in a computer for the last two categories indicated above. The representation of numbers is the subject of the next chapter.

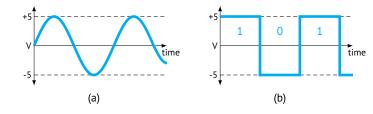

#### 2.1 Digital abstraction

Analog (or continuous) systems process time-varying signals that can take on any value across a continuous range of voltage, current or other metric, as Fig. 2.1(a) shows. The same happens with digital systems, but the difference is that one pretends that they do not! Digital systems have signals (inputs and outputs) that are represented by discrete (i.e., non-continuous) values. Fig. 2.1(b) depicts a possible waveform of a signal of a digital system. The X axis represents time, while the Y axis is the measured voltage. In this case, the system has two possible values represented by -5V and +5V. This type of system is called binary digital system. Thus, a digital signal is modelled as taking on, at any instant, only one of two possible values, which are designated as '0' and '1' (or 'low' and 'high', 'false' and 'true', 'inactive' and 'active', 'down' and 'up', etc.).

There is nothing intrinsic to the digital approach that limits it to only two values. The fundamental aspect is that the set of possible values is finite. The simplest form of digital systems is binary, where there are two possible values for the signals. The more values that must be distinguished, the less separation between adjacent values, and the less reliable is the mechanism. Thus, the binary numeral system is the most reliable method for encoding digital information, since it is easier to distinguish two possible values with physical entities than, say, five or ten. In particular, binary-coded information is the simplest one to use

Fig. 2.1 (a) analog and (b) digital waveforms.

in digital computers, since it is easy to build electronic circuits that handle two alternative conditions that can naturally code values '0' and '1'. In electronic devices, the values '0' and '1' might be physically realised by two different voltage values (e.g., 0 volts vs. +5 volts). However, these two values can be represented with other technologies: magnetic polarisation (north vs. south), electrical current (flow vs. absence), relay logic (circuit open vs. circuit closed), fibre optics (light off vs. light on), pneumatic logic (fluid at low pressure vs. fluid at high pressure). The greatest advantage of digital systems is their rigorous formulation based on mathematical logic and Boolean algebra.

The fundamental advantage of digital systems with respect to analog ones is their ability to deal with electrical signals that have been degraded by transmission through the circuits. Due to the discrete nature of the output signals, a small variation in an input value is still interpreted correctly. In analog circuits, this behaviour does not occur as a slight error at an input generates an error at the output.

Digital circuits deal with analog voltages and currents. The **digital abstraction** allows analog behaviour to be ignored, so circuits can be modelled as if they really process 0s and 1s.

#### 2.2 Bits, bytes and words

The digital abstraction hides the problems of the analog world by mapping the infinite set of real values for a physical quantity into two subsets. These two subsets correspond to two possible numbers or logic values: 0 and 1. Consequently, digital circuits can be analysed in their functionality using Boolean algebra. A logic value, 0 or 1, is often called a **bit**, a short form for binary digit.

In isolation, a single bit is not very useful, since it just permits to represent two possible values. However, if more values need to be represented, additional bits can be considered. When bits are grouped and coded, the elements of any finite set can be represented. This can be achieved by assigning some interpretation that gives meaning to the different possible bit patterns. With n bits, a maximum of  $2^n$  different entities can be represented. Groups of bits can be used to encode numbers, as explained in Chapter 3. By using a standard character code, the letters and symbols in a document can also be encoded with a set of bits. Music, images, video and other media can also be digitally represented. In fact, all information that is processed by computers is represented by patterns of bits, often long

ones. In any case, a group of bits has no meaning of its own, nor anything that intrinsically indicates what its representation is. Its meaning is given by the instructions that uses those bits.

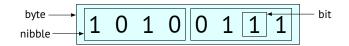

A block of 8 bits, designated as a **byte**, is the smallest addressable unit of memory in most computers. Each half of a byte is called a **nibble**, which can be represented by a 4-bit pattern or a hexadecimal digit (see Section 3.2).

Fig. 2.2 A byte.

The unit symbol for the byte is the upper-case letter B.<sup>1</sup> For multiple-byte units, it is common to use systems based on powers of 10 or 2. Unfortunately, the nomenclature for these systems has promoted some confusion. Systems based on powers of 10 use the standard prefixes (kilo, mega, giga, ...) and the respective symbols (k, M, G, ...). Systems based on powers of 2 are supposed to use binary prefixes (kibi, mebi, gibi, ...) and the corresponding symbols (Ki, Mi, Gi, ...). Table 2.1 presents the metrics for both the decimal and the binary systems.

|                                    | de                | cimal        | binary          |                   |              |  |  |  |

|------------------------------------|-------------------|--------------|-----------------|-------------------|--------------|--|--|--|

| value                              |                   | metric       | value           |                   | metric       |  |  |  |

| 10 <sup>3</sup>                    | 1000              | kB kilobyte  | 210             | 1024              | KiB kibibyte |  |  |  |

| 106                                | 1000 <sup>2</sup> | MB megabyte  | 220             | 1024 <sup>2</sup> | MiB mebibyte |  |  |  |

| 109                                | 1000 <sup>3</sup> | GB gigabyte  | 2 <sup>30</sup> | 1024 <sup>3</sup> | GiB gibibyte |  |  |  |

| 1012                               | $1000^{4}$        | TB terabyte  | 2 <sup>40</sup> | 1024 <sup>4</sup> | TiB tebibyte |  |  |  |

| 1015                               | 1000 <sup>5</sup> | PB petabyte  | 250             | 1024 <sup>5</sup> | PiB pebibyte |  |  |  |

| 10 <sup>18</sup> 1000 <sup>6</sup> |                   | EB exabyte   | 260             | 1024 <sup>6</sup> | EiB exbibyte |  |  |  |

| 1021                               | $1000^{7}$        | ZB zettabyte | 270             | 1024 <sup>7</sup> | KiB zebibyte |  |  |  |

Table 2.1 Multiple-byte units.

A machine-level program views main memory as a large array of bytes. Every byte in the memory is identified by a unique number, its address. Fig. 2.3 shows a memory with 256 locations (or cells), each one storing one byte. To specify each memory location, a 8-bit address is needed. It is important to distinguish the memory address from its contents. In the figure, the contents of memory cell 0000 0100 is 1100 0110.

A word is the basic unit of data handled by a given family of computers. The sizes of words historically range from four bits, for early microprocessors like the Intel 4004, to 60 bits, for early mainframes (CDC 6600). Modern computers have word sizes of 16, 32,

<sup>&</sup>lt;sup>1</sup> B is the symbol of the bel, a unit of logarithmic power ratio named after Alexander Graham Bell, creating a conflict. Since the bel is seldom used, little danger of confusion exists. Usually, it is used in its decadic fraction, the decibel (dB).

| 0000 0000                  | 0010 1000 |

|----------------------------|-----------|

| 0000 0001                  | 1110 1001 |

| 0000 0010                  | 0001 0000 |

| 0000 0011                  | 0100 0111 |

| 0000 0100                  | 1100 0110 |

| 0000 0101                  | 0100 1101 |

|                            |           |

|                            |           |

|                            |           |

|                            |           |

| <br>1111 1101              | 0000 0001 |

| <br>1111 1101<br>1111 1110 |           |

|                            | 0000 0001 |

Fig. 2.3 A memory with 256 locations and addresses with 8 bits.

or 64 bits. The word size is a relevant characteristic of any specific processor or computer architecture.

#### 2.3 Textual information

Text is the most common type of nonnumeric data that humans use, so computers need to represent it. In a computer, each alphanumeric character is represented by a bit pattern according to an established convention (code). The most commonly used character encoding standard is **ASCII** (American Standard Code for Information Interchange). The ASCII code is used in computers, telecommunications equipment, and other devices, and represents each character with a 7-bit string.

As Table 2.2 shows, the ASCII code includes 59 printable symbols: the digits 0 to 9, lowercase letters a to z, uppercase letters A to Z, and several punctuation symbols. Additionally, 33 non-printing control codes are considered, including for example the carriage return, the line feed and the tab. For example, lowercase j would be represented in the ASCII encoding by the 1101010 binary pattern.

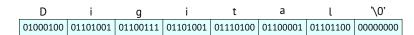

ASCII encoding uses seven bits, but in practice, characters are not stored in groups of 7 bits. Instead, one ASCII symbol is stored in a byte, with the leftmost bit usually set to 0. Different manufacturers extended the ASCII code to take advantage of the 8th bit. The general idea was to have 128 additional characters for the bit patterns whose leftmost bit is 1. A string, like for instance the English word "Digital", is encoded in the C programming language by an array of ASCII characters, terminated by the null character, whose ASCII code is '00000000'. So, this word to be represented needs eight characters, i.e., 64 bits, as depicted in Fig. 2.4.

The set of symbols provided by ASCII is too short, since there are many different symbols in the various alphabets. ASCII does not include several accents used in European languages or larger alphabets, such as Cyrillic (the Russian alphabet) and Chinese Mandarin. Thus, modern computers use **Unicode**, which is a standard for the encoding, representation, and handling of text expressed in most of the world's writing systems. It provides the

#### ESSENTIALS OF COMPUTING SYSTEMS

| binary  | char                       | binary  | char  | binary  | char | binary   | char |

|---------|----------------------------|---------|-------|---------|------|----------|------|

| 0000000 | NUL - null                 | 0100000 | space | 1000000 | Q    | 1100000  | ``   |

| 0000001 | SOH - start of header      | 0100001 | !     | 1000001 | A    | 1100001  | a    |

| 0000010 | STX - start of text        | 0100010 | "     | 1000010 | В    | 1100010  | b    |

| 0000011 | ETX - end of text          | 0100011 | #     | 1000011 | С    | 1100011  | С    |

| 0000100 | EOT - end of transmission  | 0100100 | Ş     | 1000100 | D    | 1100100  | d    |

| 0000101 | ENQ - enquiry              | 0100101 | 8     | 1000101 | Ε    | 1100101  | е    |

| 0000110 | ACK - acknowledge          | 0100110 | &     | 1000110 | F    | 1100110  | f    |

| 0000111 | BEL - bell                 | 0100111 | '     | 1000111 | G    | 1100111  | g    |

| 0001000 | BS - backspace             | 0101000 | (     | 1001000 | Η    | 1101000  | h    |

| 0001001 | HT - horizontal tab        | 0101001 | )     | 1001001 | I    | 1101001  | i    |

| 0001010 | LF - line feed             | 0101010 | *     | 1001010 | J    | 1101010  | j    |

| 0001011 | VT - vertical tab          | 0101011 | +     | 1001011 | Κ    | 1101011  | k    |

| 0001100 | FF - form feed             | 0101100 | ,     | 1001100 | L    | 1101100  | 1    |

| 0001101 | CR - carriage return       | 0101101 | -     | 1001101 | М    | 1101101  | m    |

| 0001110 | SO - shift out             | 0101110 |       | 1001110 | Ν    | 1101110  | n    |

| 0001111 | SI - shift in              | 0101111 | /     | 1001111 | 0    | 1101111  | 0    |

| 0010000 | DLE - data link escape     | 0110000 | 0     | 1010000 | Ρ    | 1110000  | р    |

| 0010001 | DC1 - device control 1     | 0110001 | 1     | 1010001 | Q    | 1110001  | q    |

| 0010010 | DC2 - device control 2     | 0110010 | 2     | 1010010 | R    | 1110010  | r    |

| 0010011 | DC3 - device control 3     | 0110011 | 3     | 1010011 | S    | 1110011  | s    |

| 0010100 | DC4 - device control 4     | 0110100 | 4     | 1010100 | Т    | 1110100  | t    |

|         | NAK - negative acknowledge | 0110101 | 5     | 1010101 | U    | 1110101  | u    |

| 0010110 | SYN - synchronize          | 0110110 | 6     | 1010110 | V    | 1110110  | V    |

| 0010111 | ETB - end transm. block    | 0110111 | 7     | 1010111 | W    | 1110111  | W    |

| 0011000 | CAN - cancel               | 0111000 | 8     | 1011000 | Х    | 1111000  | Х    |

| 0011001 | EM - end of medium         | 0111001 | 9     | 1011001 | Y    | 1111001  | У    |

| 0011010 | SUB - substitute           | 0111010 | :     | 1011010 | Ζ    | 11111010 | Z    |

| 0011011 | ESC - escape               | 0111011 | ;     | 1011011 | [    | 1111011  | {    |

| 0011100 | FS - file separator        | 0111100 | <     | 1011100 | \    | 1111100  |      |

| 0011101 | GS - group separator       | 0111101 | -     | 1011101 | ]    | 1111101  | }    |

| 0011110 | RS - record separator      | 0111110 | >     | 1011110 | ^    | 1111110  | ~    |

| 0011111 | US - unit separator        | 0111111 | ?     | 1011111 | _    | 1111111  | DEL  |

Table 2.2 The ASCII table.

Fig. 2.4 Binary pattern for the string "Digital".

capacity to represent all characters used for the written languages, since more than one million characters can be encoded. As of March 2020, Unicode has a total of 143,859 characters. Unicode 13.0 covers 154 modern and historic scripts, as well as multiple symbol sets and emoji. Unicode can be implemented by different character encodings, like UTF-8, UTF-16, and UTF-32. UTF-8 is currently the dominant encoding on the World Wide Web. Unicode is the representation scheme adopted by modern standards, such as CORBA 3.0, Java, LDAP, WML, and XML. The majority of the common-use characters fit into the first 64k code patterns, which just require two bytes (16 bits).

#### CHAPTER 2. REPRESENTATION OF INFORMATION

#### 2.4 Machine-level instructions

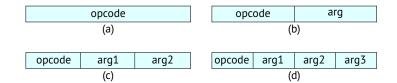

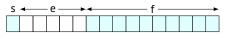

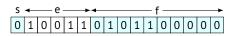

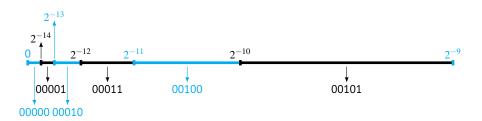

A computer program is a sequence of instructions. At the machine-level, each instruction is represented by a bit pattern. Generally, it consists of an opcode and some additional information, such as where operands come from and where to store the results. Fig. 2.5 shows several possible formats for machine-level instructions. An instruction always has an opcode to indicate what operation is to be performed. The number of arguments (or operands) varies from zero to three, depending on the instruction and on the general format considered by the specific processor.

**Fig. 2.5** Four common instruction formats: (a) Zero-argument instruction; (b) One-argument instruction; (c) Two-argument instruction; (d) Three-argument instruction.

On some machines, all instructions have the same length; on others there may be many different lengths. The opcode for each instruction type must be associated with a unique bit pattern, to identify it univocally. The instructions of the MIPS processor all have 32 bits. They are classified according to five different types (R, I, J, FR, FI). The R instructions have all the data values located in registers. The syntax of the R instructions is:

OP rd, rs, rt

where OP is the mnemonic for the particular instruction, rs and rt are the source registers, and rd is the destination register. The machine code for an R instruction has the following format:

| opcode | rs     | rt     | rd     | shamt  | funct  |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

An example of an R instruction is:

add \$t1, \$t2, \$t3

where \$t1, \$t2, and \$t3 are registers. This instruction adds the values of registers \$t2 and \$t3 and stores the result in register \$t1. This instruction is represented by the following bit pattern:

#### 000000 01010 01011 01001 00000 100000

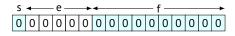

The I instructions are used when the instruction operates on an immediate value and a register value. Their syntax is:

OP rd, rs, IMM

20

where OP is the mnemonic for the particular instruction, rs is the source register, IMM is an immediate value (with a maximum of 16 bits), and rd is the destination register. The machine code for an I instruction has the following format:

| opcode | rs     | rt     | IMM     |

|--------|--------|--------|---------|

| 6 bits | 5 bits | 5 bits | 16 bits |

An example of an I instruction is an addition instruction that adds 100 to the contents of register \$t2 and stores the result in register \$t1:

addi \$t1, \$t2, 100

This instruction is represented by the following bit pattern:

001000 01010 01001 0000000001100100

#### 2.5 Images

A digital image can be represented by a grid of small points. This image is a **raster image** (or simply bitmap image) as it is seen as an array of points. Each point is called a **pixel** (short for picture element) and is represented by a binary pattern. Black and white images represent, for example, black by '1' and white by '0'. Thus, each black and white image is a set of 0s and 1s. To draw the picture, a grid must be defined and the squares coloured accordingly. If an image has size 4x6 (in pixels), then an 'A' can be drawn with by the grid in Fig. 2.6(a), whose sequence of bits from bottom to top and from let to right is 01101001 10011111 10011001.

| 0   | 1 | 1 | 0 |    | 00 | 00 | 00 | 00 |

|-----|---|---|---|----|----|----|----|----|

| 1   | 0 | 0 | 1 |    | 00 | 11 | 00 | 00 |

| 1   | 0 | 0 | 1 |    | 11 | 11 | 11 | 00 |

| 1   | 1 | 1 | 1 |    | 01 | 01 | 01 | 00 |

| 1   | 0 | 0 | 1 |    | 01 | 00 | 01 | 00 |

| 1   | 0 | 0 | 1 |    | 10 | 10 | 10 | 10 |

| (a) |   |   |   | (ł | D) |    |    |    |

Fig. 2.6 (a) Black and white image, (b) coloured image.

The size of the image needs to be stored and is part of the metadata (data about data) of an image. Other examples of metadata are the date and the time when the image was created, the name of its creator, and the type of compression used to store the image.

#### CHAPTER 2. REPRESENTATION OF INFORMATION

Adding colours to a picture entails enlarging the number of bits that are used to represent each pixel. If two bits are used, four colours can be represented. For example, if the following encoding is used ('00' white, '01' blue, '10' green, and '11' red), the image in Fig. 2.6(b) is represented by the bit pattern 00000000 00110000 11111100 01010100 01000100 10101010. Many image formats use the RGB (Red-Green-Blue) colour model. RGB has three channels to define a wide assortment of colours. RGB was originally created to represent and display images in electronic devices, such as TV sets and computers, but it has also been used in photography and digital images. If each channel has 8 bits and all channels are at 0, a pure black colour is obtained. Similarly, if all channels are at 255, an all-white colour is defined. By adjusting the red, green, and blue channels, many different colour can be defined, including grays, whites, and blacks.

The number of bits used to store each pixel is called the **colour depth**. Images with more possible colours require obviously more bits to specify each one, so they are stored in larger files. The image quality depends on the **image resolution**, which is related to how close the pixels are. It is usually measured in dots per inch (dpi),<sup>2</sup> that is, the number of dots/pixels that can be placed in a line within the span of 1 inch (2.54 cm). In a low-resolution image, the pixels are larger so fewer are needed to fill the space. This results in images that may look pixelated. An image with a higher resolution has more pixels, so it looks better when it is zoomed in. The disadvantage of having more pixels is that the file size is larger.

A vector image uses scalable shapes, such as lines and curves. Coordinates and geometry are used to precisely define the elements of the image. It is more efficient than bitmaps at storing, for example, large areas of the same colour, since it does not need to store every pixel as a bitmap image does. Additionally, a vector image can be scaled (enlarged or reduced in size), without losing quality.

#### 2.6 Audio

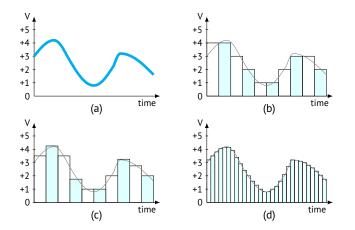

Sound waves in nature have an analog nature. To process sound (or audio), computers need to convert it into a digital format. Firstly, sound is recorded using a device, like a microphone, that translates sound waves into an electrical signal, as illustrated in Fig. 2.7(a). Then, periodic measurements of the level of that signal are registered, as shown in Fig. 2.7(b). This process that reduces a continuous-time signal to a discrete-time signal is called **sampling**. The value (or set of values) at a point in time is designated **sample**. The samples are then simply converted into binary, using a unique binary code. Afterwards, the digital sound can be processed by a computer as a sequence of bits.

The sample resolution is the number of bits used to represent the value of each sample. If more bits are available for each sample, then more levels of the signal can be captured, which improves the precision of the recording. When Fig. 2.7(b) and (c) are compared, it should be clear that the latter has higher precision. The digital sample in (b) has a low sampling resolution when compared to the digital sample in (c). The minimum step of two consecutive digital values in the former corresponds to 1 V (the value is rounded to the nearest whole number: 0, 1, 2, ...), while in the latter to 0.5 V (the value is rounded to

<sup>&</sup>lt;sup>2</sup> Other metrics also exist, like dots per centimetre and pixels per inch.

the nearest half integer: 0, 0.5, 1.0, ...). The sample in (c) is thus more accurate, i.e., it has smaller rounding errors.

**Fig. 2.7** (a) analog audio signal; digital signals with (b) a low sampling rate and a low sample resolution, (c) a high sampling resolution, (d) a high sampling rate.

The number of samples taken per second, measured in Hertz (Hz), is the **sampling rate**. The higher the sampling rate, the better the quality of the audio digital signal, because, if there are more samples, the original sound can be represented more accurately. When Fig. 2.7(b) and (d) are compared, it is clear that the latter has more quality, that is, it represents with more accuracy the original signal.

To determine the size *s* of a sound signal in bits, three values are multiplied:  $s = f \times r \times t$ . In this formula, *f* is the sampling rate in Hertz, *r* is the sample resolution measured in number of bits, and *t* is the duration of the signal in seconds.

#### Exercises

**Exerc. 2.1**: To encode Roman numbers (from 1 to 899), the following binary encoding for the symbols has been proposed: I (01), V (100), X (00), L (101), C (110), D (111). Indicate whether this encoding is valid and, if so, what Roman number is represented by the binary pattern 111101000101.

**Exerc. 2.2**: Decode the following ASCII string:

1010101 0101110 0100000 1001101 1101001 1101110 1101000 1101111.

**Exerc. 2.3**: A digital image has 128x128 pixels. Each pixel in the image stores information related to three channels (Red, Blue, Green). If each channel is capable of distinguishing 256 different tones, indicate the size in bytes of the image.

**Exerc. 2.4**: An image occupies 192 kibibytes and has dimensions of 256x512 pixels. Each pixel is represented by three unsigned integer values, which indicate the intensity of each

#### CHAPTER 2. REPRESENTATION OF INFORMATION

channel (Red-Green-Blue) in that pixel. Indicate, in binary and decimal, the maximum value that can be assigned to each of these integers, if they all have the same size.

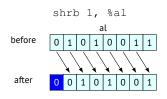

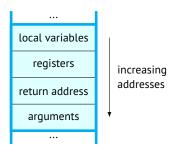

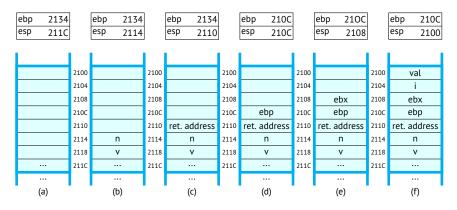

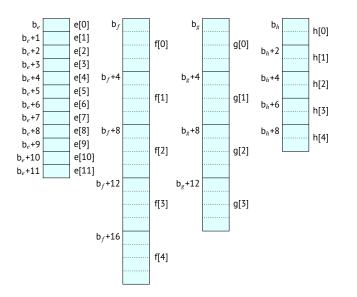

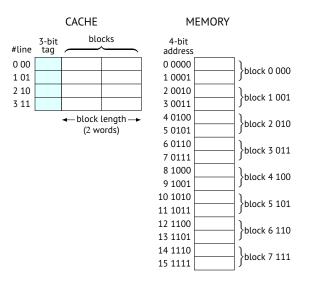

**Exerc. 2.5**: The CYMK\* subtractive colour system is formed by Cyan, Magenta, Yellow and Black and works due to the absorption of light, as the colours that are seen come from the part of the light that is not absorbed. Each pixel is represented by four 6-bit patterns that indicate the intensity in each channel. Indicate how many different colours a pixel can have, assuming that the "00000-" ("000000" and "000001") patterns cannot be used.