Universidade do Minho Escola de Engenharia

Emanuel José Rodrigues da Silva

Safety-Critical Applications in a Multicore Environment

Annipositor of Multipose During

Universidade do Minho Escola de Engenharia

Emanuel José Rodrigues da Silva

Safety-Critical Applications in a Multicore Environment

Dissertação de Mestrado Mestrado em Engenharia Eletrónica Industrial eComputadores Sistemas Embebidos e Computadores

Trabalho efetuado sob a orientação do **Professor Doutor Jorge Cabral**

#### DIREITOS DE AUTOR E CONDIÇÕES DE UTILIZAÇÃO DO TRABALHO POR TERCEIROS

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos.

Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada.

Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

Licença concedida aos utilizadores deste trabalho

Atribulção CC BY

https://creativecommons.org/licenses/by/4.0/

## Acknowledgements

First of all I would like to thanks my family, especially my parents and my brother Tiago. Without the support and the understanding of my parents this road would be absolutely much more difficult. My brother Tiago was always there setting the right path for me, calling me to reason a bunch of times even when the times went darker. For sure, those were the pillars in which I have been relying all these years.

Secondly I would like to thanks Professor Jorge Cabral for all the technical support throughout this year. It was an overwhelming year for both of us but even though we were able to work around and met a few times in order to trade some knowledge.

Last but not least, I would like to give a huge thanks to Bosch team who make this project available and give me the opportunity to work with an amazing team. It was a real pleasure to work with the Eng. 31 team.

#### STATEMENT OF INTEGRITY

I hereby declare having conducted this academic work with integrity. I confirm that I have not used plagiarism or any form of undue use of information or falsification of results along the process leading to its elaboration.

I further declare that I have fully acknowledged the Code of Ethical Conduct of the University of Minho.

### Resumo

A indústria automóvel acompanha a evolução tecnológica exponencial a que estamos sujeitos nos dias de hoje. As mais recentes novidades nos automóveis são resultado de melhorias eletrónicas (hardware & software) levando a um aumento na complexidade dos sistemas Elétricos e Eletrónicos [1]. Toda esta complexidade está passível a falhas que podem surgir pelas mais diversas razões, nomeadamente causas naturais ou deficiências de conceção/fabrico. Infelizmente é impossível eliminar todas as falhas da equação, contudo um sistema altamente confiável deve ter em conta os mais diversos cenários e reportar caso detete algo inesperado. Só assim podemos estabelecer um sistema seguro (safe). Como é que se pode medir este tipo de segurança? Um sistema seguro é aquele que não compromete a integridade física do seu utilizador ao colocá-lo em situações de risco. A industria automóvel tem este parâmetro de segurança bem presente na conceção dos seus projetos assim como nas tecnologias que usa, e o steer-by-wire não é exceção. O steer-by-wire é a inovação que vem revolucionar a próxima geração de veículos [2]. O propósito desta tecnologia consiste na substituição de componentes hidráulicos por componentes totalmente elétricos/eletrónicos no âmbito do sistema de direção do automóvel [3].

Com esta dissertação pretende-se analisar os mecanismos de *lockstep* presentes nos microcontroladores modernos e tirando partido deles, desenvolver uma arquitetura capaz de reagir a falhas fazendo uso de uma abordagem de tolerância a falhas em ambientes de multiprocessador. Esta arquitetura será usada no projeto SPA (Sensor de Posição Angular) e este projeto faz parte da tecnologia steer-by-wire. Qualquer mecanismo de tolerância a falhas é baseado em redundância [4], e é em redundância que se baseia *o lockstep* assim como se deve basear a arquitetura que se pretende desenvolver. Toda a arquitetura desenvolvida deverá a assegurar os requisitos de segurança que são característicos à tecnologia.

Keywords: Lockstep, Multicores; Segurança Critica; Sistemas Embebidos; Tolerância a Falhas.

### **Abstract**

The automotive industry has been following the exponential evolution in technology present in our days. Most of the advances seen in vehicles are the result of better electronics (hardware and software), which consequently increase the complexity of those systems [1]. No complexity is fault-free, which can arise due to many reasons, from natural causes to a mistake in the assembly process. Eliminating all the events that could lead a system to a failure state is at very least challenging if not impossible; however, with the usage of fault-tolerant approaches, the system can be surprisingly compliant with safety requirements. But how can safety be measured? A safe system is one that must not harm people, not even put them in dangerous circumstances. The automotive industry takes this safety parameter very seriously in the conception of its projects or technology that they use, and the *steer-by-wire* is no exception. The *steer-by-wire* is the innovation coming to revolutionize the next generation of vehicles [2]. The technology consists of replacing the mechanical parts of a vehicle with systems totally electric/electronic ones at the steering system of a car [3].

This dissertation aims to analyse the *Lockstep* mechanism present in recent microcontrollers and by making use of it develop a fail-operational architecture using a fault-tolerant approach for automotive applications in a multiprocessor environment. The architecture developed intends to be used within the APS (Angular Position Sensor) project, which is part of *steer-by-wire* technology. Any fault-tolerant mechanism is based on redundancy [4] and it is in redundancy that lockstep is based as must be the architecture that intends to be developed. The fail-operational architecture to be developed must be compliant with safety requirements.

**Keywords**: Fault-Tolerance; Fail-operational; Embedded Systems; Multicore; Lockstep;

# **Table of Contents**

|     | Resumo                            | V    |

|-----|-----------------------------------|------|

|     | Abstract                          | vi   |

|     | Table of Contents                 | vii  |

|     | List of Figures                   | ix   |

|     | List of Tables                    | xi   |

|     | Acronyms List                     | xii  |

| Cha | apter 1                           | 1    |

|     | Introduction                      | 1    |

|     | 1.1 Contextualization             | 2    |

|     | 1.2 Motivation                    | 3    |

|     | 1.3 Objectives                    | 3    |

|     | 1.4 Dissertation Structure        | 4    |

| Cha | apter 2                           | 5    |

|     | State of the Art                  | 5    |

|     | 2.1 Embedded Systems              | 5    |

|     | 2.2 Functional Safety             | 7    |

|     | 2.3 Dependability and Security    | . 11 |

|     | 2.4 Redundancy in Fault tolerance | . 17 |

|     | 2.5 Lockstep                      | . 19 |

|     | 2.6 Conclusion                    | . 22 |

| Chapter 3                   | 23 |

|-----------------------------|----|

| System Specification        | 23 |

| 3.1 Use Case                | 23 |

| 3.2 System Requirements     | 24 |

| 3.3 System Architecture     | 26 |

| 3.4 Hardware Specification  | 27 |

| 3.5 Conclusion              | 33 |

| Chapter 4                   | 34 |

| Implementation              | 34 |

| 4.1 Hardware Configuration  | 34 |

| 4.2 Software Implementation | 37 |

| 4.3 Conclusion              | 49 |

| Chapter 5                   | 50 |

| Tests and Results           | 50 |

| 5.1 Tests                   | 50 |

| 5.2 Results                 | 59 |

| Chapter 6                   | 61 |

| Conclusion and Future Work  | 61 |

| 6.1 Conclusion              | 61 |

| 6.2 Future Work             | 62 |

| Chapter 7                   | 64 |

| Annexes                     | 64 |

| Deferences                  | Ω1 |

# List of Figures

| Figure 2-1: Process of the hazard analysis and risk assessment     | 9  |

|--------------------------------------------------------------------|----|

| Figure 2-2: Dependability and security taxonomy                    | 12 |

| Figure 2-3: Recursive definition of faults and failures            | 14 |

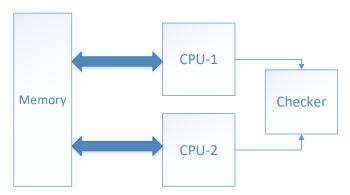

| Figure 2-4: Dual Core Lockstep (DCLS or DMR) implementation        | 20 |

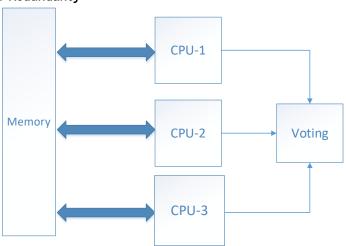

| Figure 2-5: Triple modular redundancy (TMR or TCLS) implementation | 21 |

| Figure 3-1: Application use case                                   | 24 |

| Figure 3-2: System Stack                                           | 26 |

| Figure 3-3: S32K2TV Board                                          | 28 |

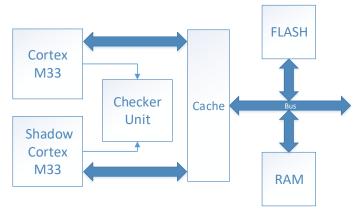

| Figure 3-4: MCU's Lockstep                                         | 28 |

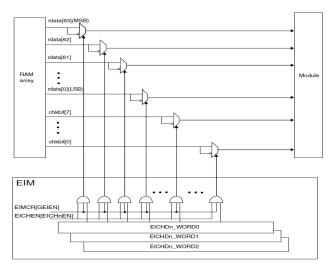

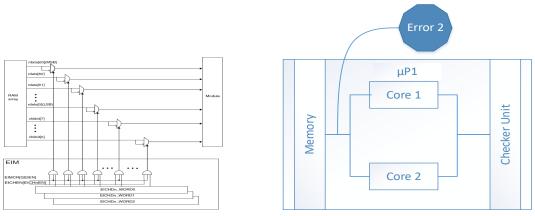

| Figure 3-5: EIM module                                             | 32 |

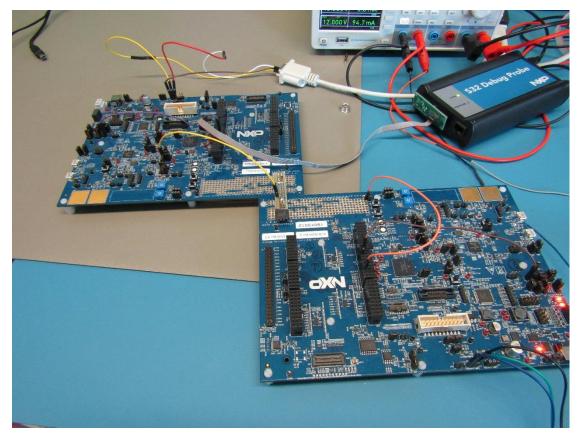

| Figure 4-1: Hardware Disposal                                      | 35 |

| Figure 4-2: Hardware Setup                                         | 36 |

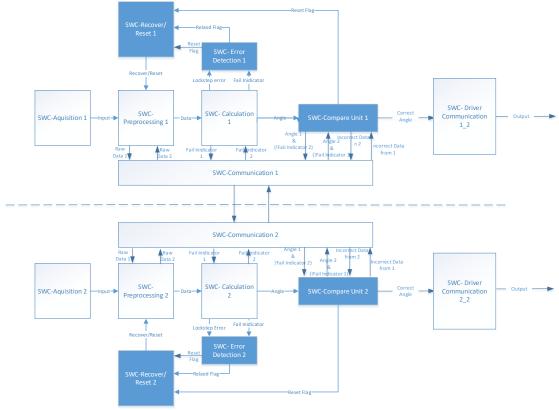

| Figure 4-3: Software block diagram                                 | 38 |

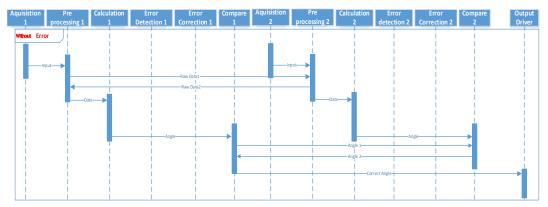

| Figure 4-4: Sequence diagram, fault free environment               | 39 |

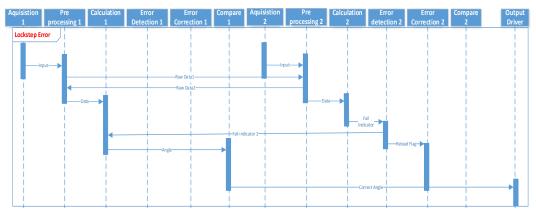

| Figure 4-5: Sequence diagram, fault at one subsystem               | 40 |

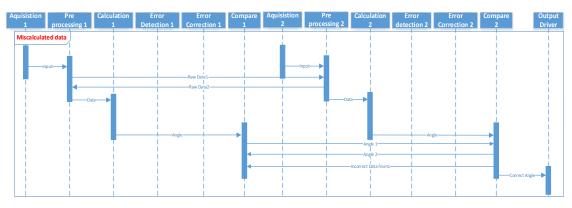

| Figure 4-6: Sequence diagram, miscalculated data                   | 40 |

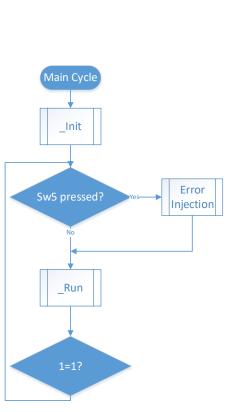

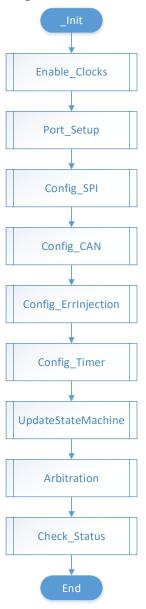

| Figure 4-7: Main Cycle flowchart                                   | 42 |

| Figure 4-8: Initialization process flowchart                       | 42 |

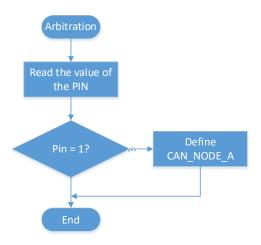

| Figure 4-9: Arbitration flowchart                                  | 43 |

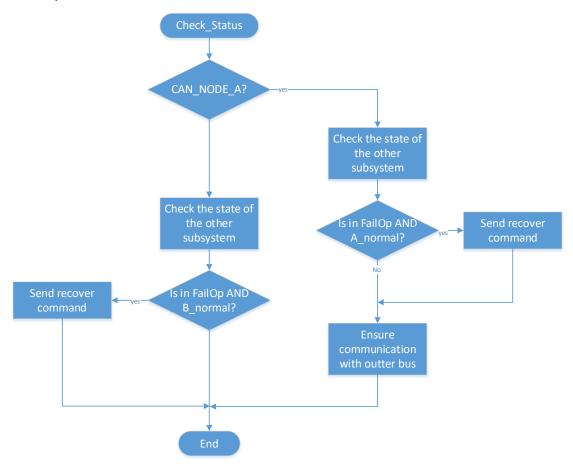

| Figure 4-10: Check status flowchart                                | 44 |

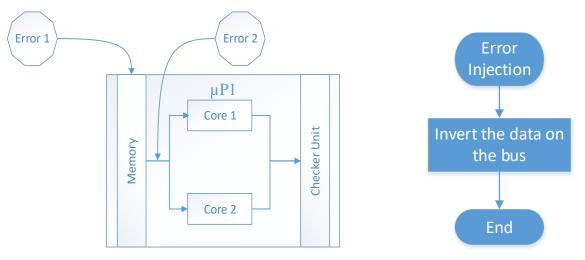

| Figure 4-11: Error Injection Scenarios                             | 45 |

| Figure 4-12: Error Injection flowchart                             | 45 |

| Figure 4-13: Run process                                           | 46 |

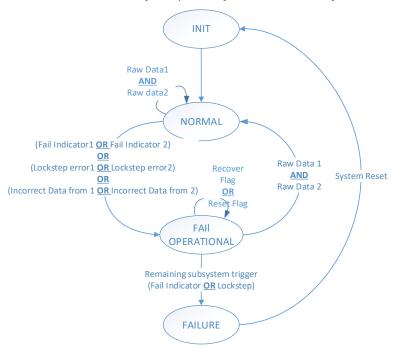

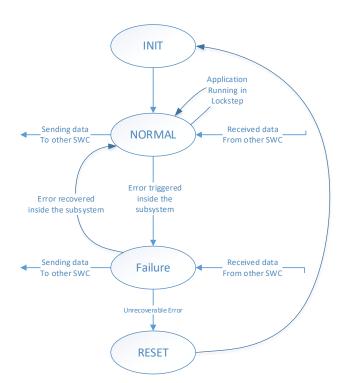

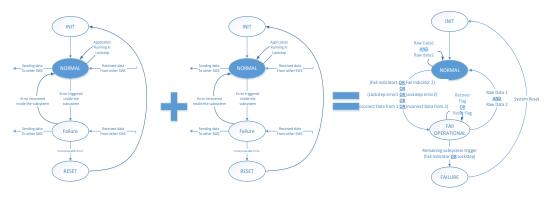

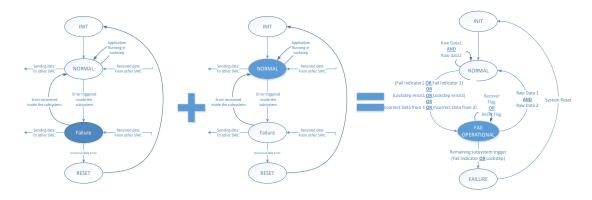

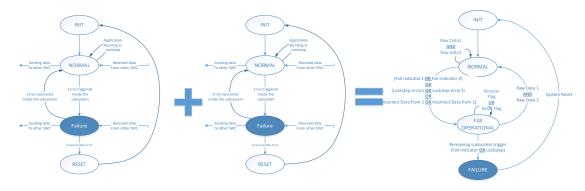

| Figure 4-14: System state machine                                  | 46 |

| Figure 4-15: Subsystem state machine                               | 47 |

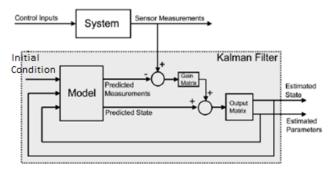

| Figure 4-16: Block diagram of Kalman filter                        | 19 |

| Figure 5-1: External communication test, time windows             | 52 |

|-------------------------------------------------------------------|----|

| Figure 5-2: External communication, fail degraded test            | 52 |

| Figure 5-3: Lockstep Error Injection                              | 53 |

| Figure 5-4: Memory Error Injection                                | 54 |

| Figure 5-5: State machine in normal state                         | 55 |

| Figure 5-6: State machine in fail operational state               | 55 |

| Figure 5-7: State machine in failure state                        | 56 |

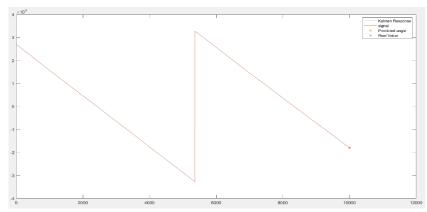

| Figure 5-8: Kalman filter test, rotating in one direction         | 57 |

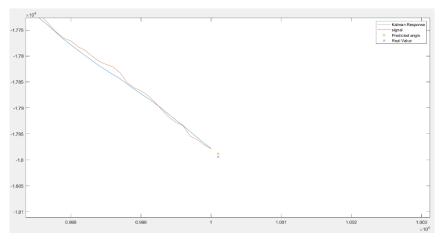

| Figure 5-9: Kalman filter test, rotating in one direction zoom in | 58 |

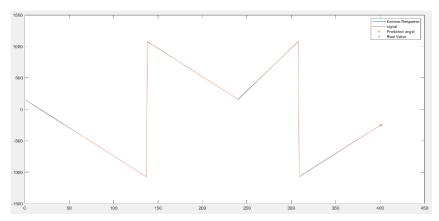

| Figure 5-10: Kalman filter test, rotating in both directions      | 59 |

# **List of Tables**

| Table 2-1: ASIL determination                                 | 10 |

|---------------------------------------------------------------|----|

| Table 2-2: Availability percentage for different system types | 13 |

| Table 2-3: Dependability Means and their use cases [25]       | 15 |

| Table 3-1: System Requirements                                | 25 |

| Table 5-1: Test Table                                         | 51 |

## **Acronyms List**

**ABS** Anti-lock Braking System. **ADC** Analog to Digital Converter. ADAS Advanced Drivers Assistant Systems. ADR Adaptive Data Rate. **AES** Advanced Encryption Standard. **API** Application Programming Interface. **APS** Angular Position Sensor. **AUTOSAR** Automotive Open System Architecture BIST Built-In Self-Test. **CAN** Controlled Area Network. CAN-FD Controlled Area Network with Flexible Data. **CPU** Central Processing Unit. **CRC** Cyclic Redundancy Check. **DCLC** Dual Core Lockstep. **DMR** Dual Modular Redundancy. **DSP** Digital Signal Processor **ECC** Error Correction Code. **ECUAL** Electronic Control Unit Abstraction Layer. **ECU** Electronic Control Unit.

**EIM** Error Injection Module.

**ERM** Error Reporting Module. **ESP** Electronic Stability Control. FCCU Fault Collection and Control Unit. FPGA Full Programmable Gate Array. **FPU** Floating Point Unit **GND** Ground. **GPIO** General Purpose Input Output. **HAL** Hardware Abstraction Layer. **IDE** Integrated Development Environment. **ISO** International Standards Organization. ISR Interrupt Service Routine. MCAL Microcontroller Abstraction Layer. MCU Microcontroller Unit. **MMR** Multiple Modular Redundancy. MTTF Mean Time to Failure. MTTR Mean Time to Repair. PIT Programmable Interrupt Timer. RTOS Real Time Operating System. SoC System on Chip. **SWC** Software Component. SWD Serial Wire Debug. TMR Triple Modular Redundancy. **TCLS** Triple Core Lockstep.

**USB** Universal Serial Bus.

## Chapter 1

### Introduction

The automotive industry has evolved, and as a result, the product that the industry delivers has been growing in complexity to provide a unique experience to the user. Every year the industry releases cars with a new set of specifications which consequently design a path for the incoming ones. In this context and focusing on the next vehicle, autonomous driving is the next step to achieve but until then there is a long way to go and a set of technologies/projects must first be developed. All those projects/technologies must be developed according to the safety and security requirements created by the International Organization of Standards (ISO), to provide a fully reliable system.

Steer-by-wire is a technology that has been developed as long as autonomous driving has been innovating. Autonomous driving relies on the success of steer-by-wire (among many other technologies) as it is impossible to drive a car without any steering system. Besides, steer-by-wire technology has great advantages such as reducing weight, and with that being done, consumes and pollute gases will be reduced as well. For that, all the hydraulic parts at the steering system used nowadays must be replaced which is the core idea of the steer-by-wire technology. To be more precise, the technology consists of the elimination of the steering column that links the steering wheel to the front axles of the car and by replacing all the mechanical actuators with electric/electronics circuitry [3]. The source of this concept comes from the x-by-wire, with origin in 1972 by NASA [5]. The "x" in x-by-wire name stands for the system in which is intended to replace the hydraulic/mechanical parts for the electronic/electric ones. Since there is a replacement of those classic components, and normally they are the ones ensuring the well-functioning of the system, even when some undesirable scenario happens (e.g. assistance steering failure), these systems must guarantee that a system failure does not lead to a state in which human life or surrounding environment are endangered. Additionally, they must ensure that a single failure of one component does not lead to a failure of the whole system [6]. These systems must base their entire architecture in redundancy, with the purpose of mitigating possible faults that could outcome from the lifecycle of it. For that reason, the concepts of safety and fail-operational must be enhanced in these types of systems.

At the processor level, there are several mechanisms that could be used to improve the safety of a system. Lockstep is one of those mechanisms. It consists of replicated processors executing the same set of instructions and compare its outputs with the purpose of finding inconsistencies between them. If the output of an instruction is different between the locked processors, then it means that a fault has occurred and must be treated in such a way that the overall system is capable to tolerate the fault.

Based on these fault-tolerant mechanisms and having in mind that the concepts of safety and fail-operational must be enhanced, this dissertation aims to develop an architecture considering all the previously mentioned. The architecture developed is to be used in APS (Angular Position Sensor), which is a sensor integrating the steer-by-wire technology. The APS is the sensor placed in the steering wheel/steering column of a vehicle and is responsible to get the intention of the user when he is moving the wheel.

#### 1.1 Contextualization

In a world where changes are constant, technological advances are a certainty, new necessities are inevitable. The necessity that comes out of the technology advance in automotive industry is to provide a fully reliable system (vehicle) which must not cause any harm in their users or surrounding environment. As one can imagine, a vehicle (the system) relies on the proper functioning of other subsystems such as the steering subsystem, braking subsystem, traction subsystem, and many others. Most of the innovations in a vehicle raises many questions regarding safety and security that must be answered. In the scope of any subsystem, safety and security measures must be fulfilled in a way not to compromise the system. Safety and security are closely interrelated concepts that pertain to the protection of lives and assets. While safety is protection against hazards (accidents that are unintentional), security is a state of feeling protected against threats that are deliberate and intentional [7]. Regarding this matter, the International Standards Organization (ISO) is developing guidelines and demands to respect those measures in the automotive field [8] that any system engineer in the automotive industry must respect.

Within this dissertation scope, safety is of extreme importance since the goal is to develop an architecture to be applied in the automotive field. As stated above, safety refers to protection against potential hazards, in other words, faults, and errors that could be causing those threats should be eliminated from the system. With that in mind, this dissertation aims to achieve a fail-operational

Chapter 1. Introduction 3

architecture. The system in which the architecture is applied, when facing faults, still needs to provide its supposed function, mitigating/tolerating faults that could lead a system to an undesirable state. It is important to note that fault tolerance is unreachable without any type of redundancy [9]. Fault tolerance approaches at the processor level are widely used in industries such as automotive and avionics [10]. For instance, in avionics, there are plenty of configurations liable to be used from TMR(Triple Modular Redundancy) to DMR (Dual Modular Redundancy). Although, TMR is the most famous among them. The proposed architecture will be using redundant hardware and lockstep mechanism to be compliant with fault-tolerant requirements avoiding common mode failures and providing the proper function of the system (APS system) even when faults are induced at the system. The Lockstep mechanism is a configuration of multicore processors where two cores (DMR) or more (TMR) are working as one. In other words, cores execute the same set of instructions and compare their outputs identifying possible inconstancies between them and reporting the case if necessary. Usually, this report is made by triggering an ISR (Interrupt Service routine). The configuration used in this dissertation was DMR, so two processor cores were used in lockstep.

#### 1.2 Motivation

Increasingly safety is nowadays a requirement in most of the daily basis commercial systems. The requirement, leads to an increase in the demand for fail-operational systems, boosting the development of new architectures and new systems with fault-tolerant capability. It opens opportunities to research distinct techniques and approaches for implementing high reliability and safety systems, which was the main motivation to embrace this research journey.

Another interesting point is that we are in the golden age of processor architectures with the appearance of processors with built-in lockstep. Thus, new approaches must be thought of to use this fault tolerance mechanism.

All together with the high demands on the industry for these types of features give the necessary motivation to pursue and develop new architectures enabling the system to be fully fail-operational.

#### 1.3 Objectives

After taking into consideration the motivation, this dissertation aims to develop a fail-operational architecture to be used within the APS project. This fail-operational architecture covers the acquisition and calculation of the angle of the steering wheel. Therefore, the main goals of this dissertation are as follows:

- Analysis of architectures and fault tolerant mechanisms in the case of study;

- Analysis of software architectures;

- State machine design in a way to react to possible faults;

- Software implementations according with certification ASIL-D of standards ISO 26262;

- Driver elaboration liable to be used in AUTOSAR software architecture;

- Tests and validation of the architecture;

#### 1.4 Dissertation Structure

This document is structured in six chapters, and its structure follows a logical order according to the development process that occurred during this Master's Thesis.

The first chapter introduces the current technological concepts, referring to the context and the motivation for the development of this project, as well as its objectives.

The second chapter explores the concepts which are the basis of this project, and thus gives a more in-depth overview of safety and dependability in systems. It is also mentioned in this chapter The State of the Art for the different kinds of lockstep mechanisms that exist and are considered for use in this project.

The third chapter gives an overview of the system and a further selection of which components were chosen and the reasoning for their choices.

The fourth chapter is divided into two sections corresponding to the hardware and software implementations. It focuses on how this project was developed and explains the path taken.

Chapter five describes the tests that were made, along with some considerations about the obtained results.

Chapter six presents the main conclusions relative to this project, as well as future improvements to the proposed architecture.

## Chapter 2

### State of the Art

To develop a fail-operational architecture, some technological concepts need to be understood. It is crucial to fully understand the relevance of safety, dependability concept, the redundancy, lockstep mechanisms, and the different existing implementations.

After knowing what a lockstep configuration is composed of and its architecture, it is then possible to make further studies on which type of configuration to use.

This chapter presents a technological overview and discussion on the topics previously mentioned.

#### 2.1 Embedded Systems

Embedded systems are usually everywhere executing several daily tasks, despite often being unnoticed. They can have different sizes and complexities, from a television or even a printer to a smartwatch. Usually, interacting with the outside world through sensors (input), actuators (output), and in some cases, using an interface to the user like an LCD or even a LED, an embedded system characterizes for having hardware and software combined to accomplish a specific task. In many circumstances, it could have mechanical parts to help it with that particular job [11]. Due to their assignment, an embedded system must be application-oriented; this means that engineers that design them must project it with the strictly necessary resources for their application to optimize variables like cost, power efficiency, weight, and performance. However, as an embedded system has requirements and constraints that must be respected, it is necessary to have a trade-off between management and usage of resources. Examples of embedded systems with strong constraints are the ones that have time restrictions, classified as soft and hard real-time. The soft real-time embedded systems are the ones that, if missing a deadline, there is not much harm for the system in what it was incorporated it is somehow allowed to miss a deadline as it is in the case of video streaming. However, in hard real-time, a missed deadline could lead to a catastrophic event as it happens in the Antilock Braking System (ABS) of a car.

Despite everything mentioned, embedded systems must be reliable, assuring the well-functioning in all situations; resilient, backing to a safe state even after the occurrence of a fault; safety and secure, being fault-tolerant and having secure communications. The simple embedded systems usually are programmed without layers of abstraction, in other words, directly in their logic hardware (bare-metal programming). However, with the rising complexities in systems, the usage of an operating system has become fundamental.

#### 2.1.1 Elements of an Embedded System

At the architectural level, an embedded system represents the interaction between hardware and software elements, whose details are hidden in a way to have only information about the behavioural and relational levels. These elements can be internally implemented in the embedded system device or externally implemented interacting with the internal elements as well as with the external environment [12].

An embedded system is generally composed of basic elements necessary to the execution of code, internals peripherals, communication interfaces, and the respective software. In a generic form, an embedded system has the following elements:

- Central Processing Unit: Responsible for the execution of code, making the logic and control

operations as the entrance and exit of data;

- Random Access Memory (RAM): It is a volatile memory of quick access used to store temporarily the variables needed for the execution flow of code;

- Flash Memory: It is a non-volatile memory with access being slower than the access to RAM.

Used to store data permanently like the code responsible for the boot of the system, operating system code, programs, and file system;

- Communication Peripherals: An embedded system frequently uses communication protocols like the Universal Serial Bus (USB), RS232, and Ethernet for which there is peripheral existent;

- Input & Output Devices: As referenced before, an embedded system interacts with the outside

world and may or may not have an interface with the user. Some peripherals like Analog-toDigital-Converter (ADC), audio controllers, General Purpose Input Output controllers (GPIO),

among many others, are also in an embedded system.

#### 2.2 Functional Safety

The complexity of today's systems is, for the most, due to electronic and electric (E/E) systems. E/E systems have a major role to play in our daily lives making our tasks easy to accomplish. However, those systems when badly designed could have a terrible effect, possibly causing harm and injuries to those who are using them. The vehicle of today is a product of that complexity and innovation in E/E systems. It is believed that most of the innovation that we see in newer cars is based on the innovation experienced at ECUs that a car contains [13]. Nonetheless, it is important to highlight those electronic devices are not perfect and fault-proof. As addressed previously, when the system is made over a faulty design a high probability exists that it could cause serious damage, especially in a vehicle. With that in mind, the International Organization of Standards was in an inevitable necessity to create some standards regarding functional safety in E/E systems in the automotive domain, the ISO 26262 [8].

#### 2.2.1 Introduction to safety standards

As previously mentioned, the ISO26262 [8] is an international standard focusing on the safety of automotive electrical/electronic systems. Divided into 12 documents, covering the entire product development lifecycle, and designed to ensure that systems developed for road vehicles are composed with an appropriate level of rigor required for their intended application. The standard applies additional constraints to the process of development, focused on the system safety aspects. Safety means one must not harm others. A safe system is one that does not cause harm to people. Of course, no system can be made completely safe, so safety is about an attempt to reduce the potential for harm to an acceptable level. ISO26262 takes a risk-based approach to manage potential harm (often referred to as residual risk), based on three factors:

- Severity: the potential harm;

- Exposure: the probability of occurrence;

- **Controllability**: the ability of the system to avoid the specified harm.

In other words, risk, as defined in the standards is a combination of the probability of occurrence of harm and the severity of that harm.

Thus, the standards organize the risk into four Automotive Safety Integrity Levels (ASILs). ASIL A is the lowest level while level D is the highest one. For instance, a system classified as ASIL A is Cruise Control. This one may cause inconvenience or minor injury to the driver, which means that the severity is low. On the other extreme, on the ASIL D level, is the electric steering system. This system has the potential to cause significant harm by providing the wrong level of assistance, feedback, or even

completely incorrect output. Later in this document a detailed insight of the ASIL classification is approached.

For this dissertation, the author will just be considering 6 of those 12 parts that compose ISO26262, meaning that some of the subjects covered by the standards will not be addressed. For example, the conception of hardware is not a concern for this dissertation since all the hardware that will be used has already been developed and it is certified as a specific level of rigor for the task that is assigned. The only hardware that it is intended to develop is concerning the communication protocol and it is going to be addressed later in this document. With that said, the parts considered are [14], [15], [16], [17], [18], [19]:

- Part 1: defines the language of ISO262626;

- Part 2: is an over-arching guide focusing on the management of safety requirements, both from

a project and organizational point of view;

- Part 3: focuses on what the standards call the concept phase. This phase is considered with

initial project definition, establishing the safety requirements and criteria for the project and

initiating the safety lifecycle;

- Part 4: is concerned with system level development, that is, detailed requirements analysis, system synthesis, functional and logical allocation, and system evaluation, validation and verification;

- Part 6: focuses on the software aspects of system design and implementation;

- Part 9: gives requirements and guidance with respect to safety analyses. In particular with all

aspects related to ASIL-oriented requirements.

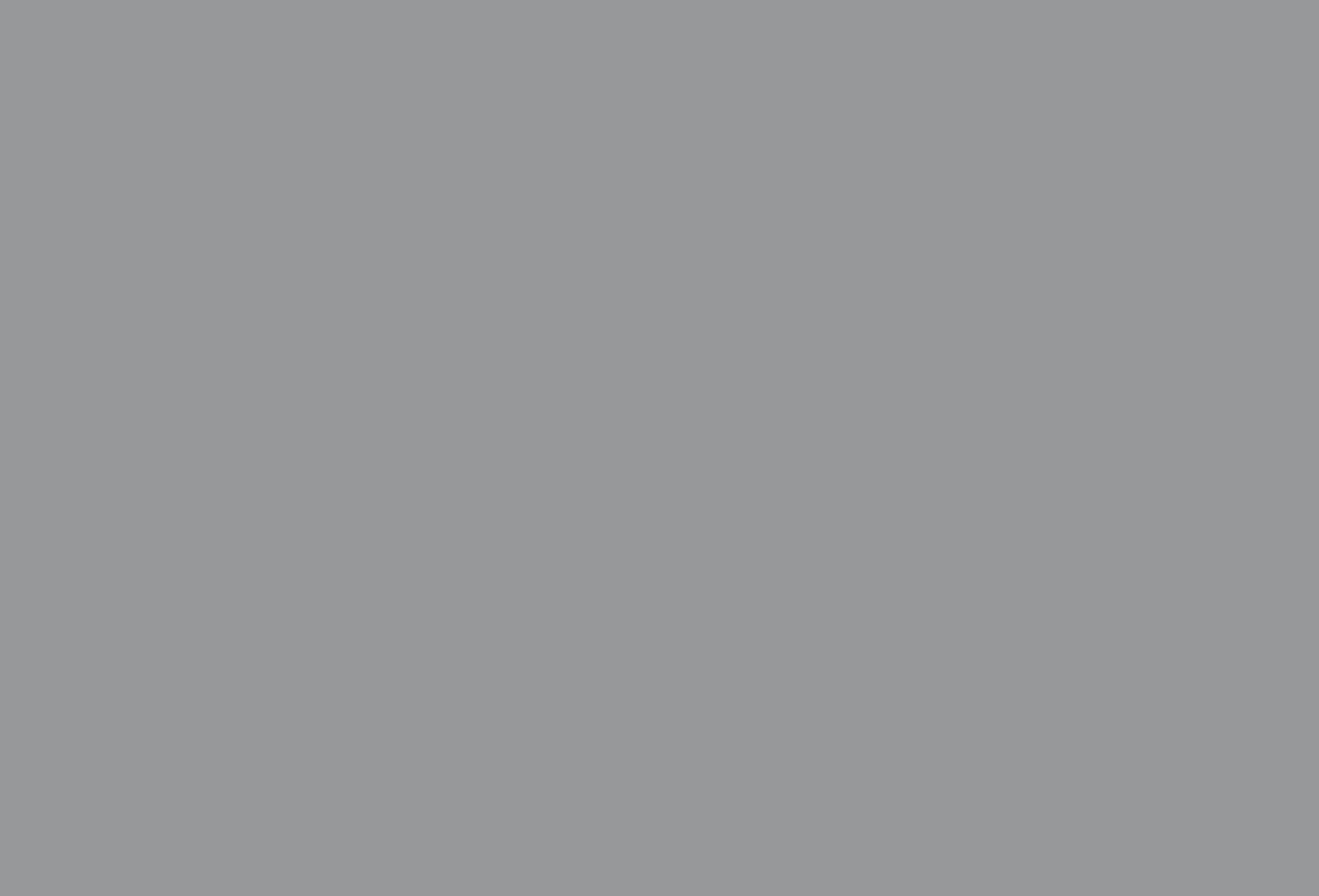

#### 2.2.2 ASIL classification and decomposition

To have a better understanding of how the ASIL and safety goals are determined, Figure 2-1 and Table 2-1 can be used. As addressed in the previous chapter, in [8] the guidelines to develop a system in a way to decrease the residual risk of it are described. According to the standards, the residual risk (RR) is a product of the potential harm (C) with the probability of occurrence (E) with the severity (S). Residual Risk can be defined as RR = C\*E\*S. This equation can be better understood by referring to Figure 2-1 since it depicts the process of hazard analysis and risk assessment. The letters used in the equation stands for the three parameters, in which the residual risk is calculated, Exposure, Controllability, and Severity. Regarding these parameters there are different levels that describe different situations that a system can face.

- **Severity**: describes the extent of the harm from S0 (no harm to any person) to S3 (severe injuries, survival uncertain);

- Controllability: represent the probability that the driver, passengers or surrounding environment can avoid the specific harm, from CO (no harm to any person) to C3 (difficult to control or uncontrollable);

- Exposure: describes the probability of being in that particular situation from E0 (unlikely to be) to E4 (highly probable).

Figure 2-1: Process of the hazard analysis and risk assessment

Table 2-1 has all the combinations possible in a way to establish which are the best safety goals for a specific system. As it can be seen in the table ASIL has a classification from A to D describing the safety goals for a system but besides those four levels, there is also another unit described as QM (Quality Management). The level QM denotes that it is not required to cope with the requirements of the [8], quality management is sufficient.

| Severity Class | Exposure Class | Controllability class |    |    |

|----------------|----------------|-----------------------|----|----|

|                |                | C1                    | C2 | C3 |

| S1             | E1             | QM                    | QM | QM |

| S1             | E2             | QM                    | QM | QM |

| S1             | E3             | QM                    | QM | Α  |

| S1 | E4 | QM | Α  | В  |

|----|----|----|----|----|

| S2 | E1 | QM | QM | QM |

| S2 | E2 | QM | QM | Α  |

| S2 | E3 | QM | Α  | В  |

| S2 | E4 | Α  | В  | С  |

| S3 | E1 | QM | QM | Α  |

| S3 | E2 | QM | Α  | В  |

| S3 | E3 | Α  | В  | С  |

| S3 | E4 | В  | С  | D  |

Table 2-1: ASIL determination

Despite specifying restrict rules, in [8] also exists a bit of flexibility in the ASIL classification. According to [19], the standards allow the designer to benefit from a sufficiently independent redundant architecture. ASIL decomposition is a measure to comply with systematic failures by decomposing a single safety requirement into two sufficiently independent requirements and by implementing those requirements in two independent architectural elements. The benefit is the resulting two requirements founded have lower ASIL classification than the initial one. The key principle is if two independent architectural elements are performing the same function then the probability of both failing simultaneously is lower even if their safety integrities are lower than that of the original requirement.

In [19], the following decomposition schemes:

- ASIL D

- ASIL D = ASIL B (D) + B (D)

- ASIL D = ASIL C (D) + A (D)

- ASIL D = ASIL D (D) + QM (D)

- ASIL C

- ASIL C = ASIL B (C) + A(C)

- ASIL C = ASIL C (C) + QM (C)

- ASIL B

- ASIL B = ASIL A (B) + A (B)

- ASIL B = ASIL A (B) + QM (B)

- ASIL A

- ASIL A = ASIL (A) + QM (A)

This decomposition can be applied to any level of the system. Hardware components can have this procedure as well as the software components. This can even be used recursively.

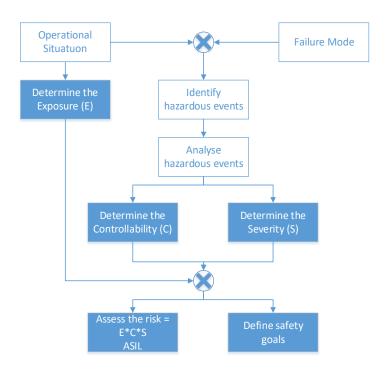

#### 2.3 Dependability and Security

Dependability is the ability to deliver service that can justifiably be trusted. However, this definition leads to a problem related to the trust's definition, and that is where the definition of security enters [20]. Security and dependability are highly correlated as is going to be addressed throughout this chapter. Therefore, those concepts must be understood before any development on a safety critical application due to the importance that they have. A dependable and secure system has attributes with which the system is measured, it has threats that compromise the functionality of the system and, finally, it has the means to eliminate these threats. In Figure 2-2, an overview of the taxonomy is depicted in a graph. Throughout this chapter, every element of the tree represented will be explained.

#### 2.3.1 Attributes

The dependability attributes define the properties that a system is expected to have [21]. According to [20], the attributes are composed by: (1) availability, readiness for correct service; (2) reliability, the ability of the system to deliver a correct service continuously; (3) safety, absence of catastrophic consequences to the system external environment, both for the user and the environment; (4) integrity: absence of improper system alterations; (5) maintainability, ability to undergo modifications and repairs. When addressing security, an additional attribute has a great prominence, confidentiality. Confidentiality is defined by the absence of unauthorized disclosure of information. It can be concluded that dependability attributes are a subset of abilities that a system must have to provide the correct service. In [22] is said that dependability attributes are a subset of the non-functional properties that must be specified, analysed, and verified during the system development process. For that reason and according

to [21] and [23], this subchapter is going to focus on the three main attributes, reliability, availability and safety.

#### 2.3.1.1 Reliability

According to the literature, reliability describes the ability of a system to function under stated conditions for a specified period of time [21]. It can be described by a mathematical function given a period of time and given that at the initial the system was in working conditions. The function describes the probability of the system to operate without a failure in the interval. By expressing this attribute in a

Figure 2-2: Dependability and security taxonomy

mathematical way is it possible then to express the Mean Time to Failure (MTTF). The MTTF is the expectation of the time at which the system will fail. If a system is highly reliable it means that MTTF is larger when compared to MTTR then availability is close to 100% [9].

#### 2.3.1.2 Availability

Availability of a system, likewise reliability, can be expressed by a mathematical function. Similarly, it expresses a probabilistic function that attempts to guess whether the system is functioning or not at the instant of time specified [21]. As stated above for high values of availability, meaning that the system for the most of instants is working as it should, MTTF values should also be larger. Therefore, for smaller MTTF values, availability varies significantly with repair time, the MTTR. The Mean Time to Repair (MTTR), is the expectation of the time to restore a failed system to correct operation. [9] [24]. For that reason, there is another concept that it is important to have in mind, which is undoubtedly related with availability, it is the downtime per year. It represents the amount of time in a year where the system is inoperable.

Said that, it can be deduced that a safety-critical must have a high availability and low downtime per year. Table 2-2 represents the availability and downtime per year for different systems ratings.

| System Rating   | Availability | Downtime     |

|-----------------|--------------|--------------|

| Routine         | 99%          | 3.65 days    |

| Essential       | 99.9%        | 8.77 hours   |

| Critical        | 99.999%      | 5.26 minutes |

| Safety-Critical | 99.99999%    | 3.16 seconds |

Table 2-2: Availability percentage for different system types

#### 2.3.1.3 Safety

In [20] is considered that safety refers to the absence of catastrophic consequences on the users and the environment. For that reason, systems where the functionalities have a critical safety variable this concept is very important. There is a great deal of systems that have safety critical ratings, such as, avionics, power plants and pacemakers. The reason why is mostly because of the definition made in [20]. These systems when facing a fault must not compromise the user that is why when they have these safety-critical ratings they must also have a definition of safe state. The definition of the term safe state leads to the different behavioural models a system can incorporate in the presence of failures. These terms are quite controversial since they have many interpretations. Here the terms according to [13] are going to be presented.

- Fail-operational systems remain functional in case of a subsystem failure.

- Fail-silent systems enter a state that does not interfere with other safety related systems in case of a failure.

- Fail-safe is, if after one or several failures, the system is brought to an active or passive safe state.

#### 2.3.2 Threats

The threats represent in a system context, situations that could lead the system to an erroneous state.

These threats are usually referred as errors, fails and, failures. They can come from the most various causes, from an error at the assembly process to an error happening at the run time

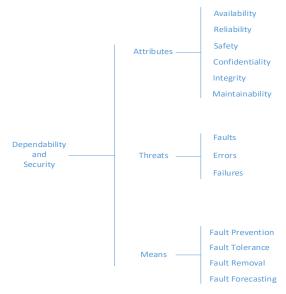

#### 2.3.2.1 Fault, Error, Failure

Regarding the definition of faults and failures, this thesis will focus on the definitions of the [14] and the recursive interpretation of the [19]:

- Fault is an abnormal condition that can cause an element or an item to fail.

- Error is discrepancy between a computed, observed or measured value or condition, and the true, specified or theoretically correct value or condition.

- Failure represents termination of the ability of an element, to perform a function as required.

The recursive definition mentioned, that the terms fault and failure can be used recursively, is shown in Figure 2-3.

Figure 2-3: Recursive definition of faults and failures

Faults and failures can be categorized based on their origin as systematic- or random HW faults. Systematic faults and failures are deterministic. They can be eliminated only by improving the design or the production process. Typical causes for systematic failures are poor design (e.g. wrong SW specification) or manufacturing-related issues (e.g. contaminated soldering). Random HW failures on the other hand occur in an unpredictable manner. They are mainly caused by ageing or environmental factors. It is obvious that SW is prone to systematic failures only.

Another classification of faults is based on their temporal behaviour. Permanent faults occur and remain until removed or repaired. Transient faults, on the other hand, occur and disappear subsequently. Transients can occur in HW elements for example due to cosmic radiation. Related to the terms of faults and failures are the often misunderstood, hazard and hazardous event. A hazard is defined in [8] as potential source of harm. Only those failures can be hazards, where there are operational situations, in which the failure can lead to an accident. A hazardous event is exactly this failure (= hazard) combined with this unfavourable operational situation. For example, unintended gear change from the 5th to the 2nd is harmless when the vehicle is coasting at 60 km/h in a straight line. But the very same failure mode can lead to an accident when occurring during high speed cornering.

#### 2.3.3 Means

Dependability means are the methods and techniques enabling the development of a dependable system. As it can be seen in Figure 2-2, there are four different means. During this chapter it is intended to address all of them but with more focus on fault tolerance since this dissertation will make use of that mean. It is important to note that the different means represented in Figure 2-2 take their role in different phases of the product lifetime. For that reason, before getting into the concepts, a table is presented where each mean makes sense to enter. In Table 2-3 the system lifetime is divided in two groups where pre-service consists in the development phase and the in-service represent the phase where the system is already commercialized and it is in operational conditions. Each mean has correspondent assignment in the table. If a "tickle" is presented in front of the mean, could be said that the appliance of that mean make sense at that phase of lifetime. On the other hand, if it has an "x" it means that the mean is not applicable on the phase.

| Means             | System Lifetime Phases  |                        |  |

|-------------------|-------------------------|------------------------|--|

|                   | Pre-Service             | In-Service             |  |

| Fault Preventing  | Design & Implementation | ×                      |  |

| Fault Removal     | Test & Debug            | Preventive Maintenance |  |

| Fault Forecasting | ✓                       | ✓                      |  |

| Fault Tolerance   | ×                       | ✓                      |  |

Table 2-3: Dependability Means and their use cases [25]

#### 2.3.3.1 Fault Preventing

Fault prevention means to prevent the occurrence or introduction of faults [20]. It is achieved by quality control techniques during specification, implementation, and fabrication stages of the process. For hardware, this includes design reviews, component screening, and testing. For software, this includes structural programming, modularization, and formal verification techniques [26]. A rigorous design review and well elaborated set of tests may eliminate specification faults. If it is efficiently tested many of its faults and component defects are avoided.

#### 2.3.3.2 Fault Removal

Fault removal means to reduce the number and severity of faults [20]. It is performed during the development phase as well as during the operational life of a system. During the development phase,

fault removal involves three steps: verification, diagnosis, and correction. Fault removal during the operational life of the system consists of corrective and preventive maintenance.

Verification is the process of checking whether the system meets a set of given conditions. If it does not, the other two steps follow: the fault that prevents the conditions from being fulfilled is diagnosed and the necessary corrections are performed. In preventive maintenance, parts are replaced, or adjustments are made before failure occurs. The goal is to increase the dependability of the system over the long term by staving off the ageing effects of wear-out. In contrast, corrective maintenance is performed after the failure has occurred in order to return the system to service as soon as possible [21].

#### 2.3.3.3 Fault Forecasting

Fault Forecasting means to estimate the present number, the future incidence, and likely consequences of faults [20]. It is done by performing an evaluation of the system behaviour with respect to fault occurrences or activation. The evaluation can be qualitative which aims to rank the failure modes or event combinations that lead to system failure or quantitative, which aims to evaluate in terms of probabilities the extent to which some attributes of dependability are satisfied. Simplistic estimates merely measure redundancy by accounting for the number of redundant success paths in a system. More sophisticated estimates account for the fact that each fault potentially alters ability of the system to resist further faults [21].

#### 2.3.3.4 Fault Tolerance

According to the threats approached in 2.3.2.1 a fault is a malfunction in one component. That malfunction can lead the affected component malfunctioning which may propagate to a failure. Fault tolerance means to avoid service failures in the presence of fault [20]. Fault tolerance is achieved by using some kind of redundancy. The redundancy allows a fault either to be masked or detected. This terms of detection and masking will be addressed in detail in this subchapter while the importance of redundancy in fault tolerance is approached on the next chapter. First, before getting to know what detection and masking are, it is important to highlight that redundancy alone does not make a system fault tolerant. For instance, two components duplicated and connected in parallel do not make a system fault tolerant, for that it is necessary to have monitoring and processing analysing the results and selecting the correct one. For that reason, masking and detection are important.

Fault masking is the process of ensuring that only correct values get passed to the system output despite the presence of a fault. This is done by preventing the system from being affected by errors by either correcting the error, or compensating for it in some way [27]. Since the system does not show the impact of the fault, the existence of the fault is invisible to the user/operator. For example, a memory protected

by an error-correcting code (ECC) corrects the faulty bits before the system uses the data. Another example of fault masking is triple modular redundancy with the majority voting [28].

Fault detection is the process of determining that a fault has occurred within a system. Examples of techniques for fault detection are acceptance tests and comparison. An acceptance test is a fault detecting mechanism that can be used for systems having no replicated components. Acceptance tests are common in software systems [29]. The result of a program is subjected to a test. If the result passes the test, the program continues execution. A failed acceptance test implies a fault [30]. Comparison is an alternative technique for detecting faults, used for systems with duplicated components. The output results of two components are compared. A disagreement in the results indicates a fault.

Fault location is the process of determining where a fault has occurred. A failed acceptance test cannot generally be used to locate a fault. It can only tell that something has gone wrong. Similarly, when a disagreement occurs during the comparison of two modules, it is not possible to tell which of the two has failed. Fault containment is the process of isolating a fault and preventing the propagation of its effect throughout the system. This is typically achieved by frequent fault detection, by multiple request/confirmation protocols and by performing consistency checks between modules.

Once a faulty component has been identified, a system recovers by reconfiguring itself to isolate the faulty component from the rest of the system and regain operational status. This might be accomplished by having the faulty component replaced by a redundant backup component. Alternatively, the system could switch the faulty component off and continue operation with a degraded capability.

#### 2.4 Redundancy in Fault tolerance

There are various approaches to achieve fault tolerance. Common to all these approaches is a certain amount of redundancy. For our purposes, redundancy is the delivery of functional capabilities that would be unnecessary in a fault-free environment [31]. This can be a replicated hardware component, an additional check bit attached to a string of digital data, or a few lines of program code verifying the correctness of the program results. The idea of incorporating redundancy in order to improve the reliability of a system was pioneered by John von Neumann in [32]. Two kinds of redundancy are possible [33]: space redundancy and time redundancy. Space redundancy provides additional components, functions, or data items that are unnecessary for fault-free operation. Space redundancy is further classified into hardware, software, and information redundancy, depending on the type of redundant resources added to the system. In time redundancy the computation or data transmission is repeated and the result is compared to a stored copy of the previous result. The reason why this is called time

redundancy is due to the fact that this specific technique need significantly more time to have the outputs produced. In order to clarify those concepts, each one is going to be addressed in the next subchapters. Either way, it can be said beforehand that redundancy is not for free, it adds additional resources to systems to improve its reliability. Extending system about one more computer, or doubled available memory, may drastically complicate the system design. Performance, weight, size of the system may be affected, as well as the cost of design and implementation. Appropriate redundancy method must be selected to achieve the goals of the system [34].

#### 2.4.1 Space Redundancy

As previously mentioned, this technique integrates the categories of hardware, software, and information redundancy. All of these categories are achieved by replicating or adding additional components that are unnecessary for the execution of a certain task.

In hardware redundancy the hardware components are replicated in order to cooperate among themselves. Both have the purpose of achieving the same task and they are only added to mitigate the fault scenarios. Taking the computer system example, the hardware redundancy is made through two or more independent computers with their own processor, memories and peripherals. The computers systems are able to cooperate in three ways, according to its implementation: Statically; dynamically or in a hybrid way. In a static implementation all the computers are working in parallel and comparing the results calculated. If inconsistencies appear it means that a fault occurred in one of the subsystems, and the correct output is chosen with a predefined algorithm [35]. In dynamic form only one computer subsystem is working and if it fails then another computer is started to continue the system task. The hybrid implementation uses a combination of both previously addressed implementation, static and dynamic approaches.

Software redundancy uses replicated code for the same function that is intended to deliver. This technique of software redundancy replicates the code to get a compiled redundant machine code that owns different instruction for the same purpose. This software redundancy technique is also known as instruction redundancy. This name is attributed due to the additional instructions that are added to the binary code whenever a spare code is added to the application code. In the spatial redundancy, one part of the code is replicated, e.g., variables or functions. After the replicated code is executed the replicas are compared and checked if they are all equals. If it is not the case, then an error has occurred.

Information redundancy consists of using additional information which is not required to perform the task in question. For instance, the Error Correction Code (ECC) is an additional value attached to the

information content of a memory and it is not required to execute the software task. Nevertheless, it allows to check data correctness and may also be used to correct corrupted data. Another great example of information redundancy is the data backup that everyone is familiar with by using the so famous cloud. The same information is duplicated to reduce the possibility of data loss.

As time redundancy, space redundancy is suitable to deal with transient faults since it is very unlikely to occur in the same memory region twice. For example, if a variable is replicated when it is affected by an error, it is possible to detect and correct it through comparison with the other redundant variables.

#### 2.4.2 Time Redundancy

This technique consumes additional time to get a correct and valid result. In the time redundancy, one specific part of the code is re-executed more than once. Execution results are stored and at the end of all program executions, the stored results are compared. The outputs are verified if they match the execution went as it should, if they do not, it is because an error has occurred. This kind of redundancy in software is suitable to deal with transient faults since they do not occur (or are very unlikely to occur) in the same location twice and cause the same error consecutively. So, the re-execution of the same code should not produce the same transient fault which will be mitigated.

#### 2.5 Lockstep

Lockstep is a fault tolerance technique that uses hardware redundancy at the processor level. Its implementation can differ by the number of replicated cores used as well as by the error recovery techniques that the cores employ. The configuration of redundancy used at this level is static, which means the working principle consists of, having each processor used running at the same time, or in some cases with a delay of one or few clock cycle in the same instruction, then the outputs produced are compared in order to identify possible inconsistencies between cores without even the possibility of changing the implementation. When the inconsistencies appear, it means that some error has occurred. Therefore, since a fault tolerance mechanism is being used, which is the lockstep the error must be treated in order not to propagate it to the whole system and not change the fault into a failure.

During this chapter the different implementations of lockstep that were found interesting are going to be presented for the understanding of this dissertation and after getting to know the implementations the error recover techniques will also be presented.

#### 2.5.1 Lockstep Implementations

Regarding lockstep implementations they can be differed by the way the checker (the unit responsible for finding inconsistencies) is performed and by the number of cores that they use, as it was mentioned previously. Besides, it can have a loosely- or tightly coupled- implementation. In the tightly-coupled hardware lockstep, the processors are running synchronously and the outputs are compared instruction by instruction. The comparisons are continuously being made. An error is detected before it propagates to the outside of the system (causing a failure). This type of lockstep is more robust as the granularity is small. However, it is expensive to implement [36]. In a loosely-coupled implementation, the checker is made with less frequency when compared to the tightly implementation. This does not ensure that each instruction is executed properly, but errors are caught before they are allowed to leave the processors and propagate to other devices. This can also lead to performance boosts over tightly-coupled lockstep designs because fewer comparisons are performed [37]. Due to this, the error detection is weaker. In what concerns the way the checker is performed, the type of the lockstep should be chosen according to the type of application, its safety-critical requirements, and the hardware system constraints.

Now, when it comes to the number of CPU cores used in this technique, there is a great deal of possible implementations combining architectures of lockstep. For the purpose of this dissertation only the Triple Modular Redundancy (TMR) also known as Triple Core Lockstep (TCLS) and the dual modular redundancy (DMR), often called Dual Core Lockstep (DCLS), will be addressed.

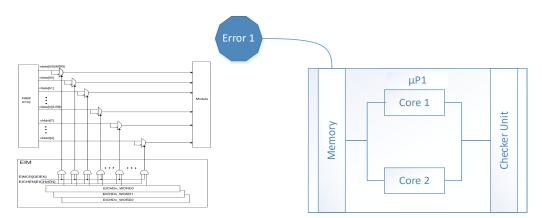

Figure 2-4: Dual Core Lockstep (DCLS or DMR) implementation

#### 2.5.1.1 Triple Modular Redundancy

In the TMR configuration (Figure 2-5) three identical CPUs execute the same code in lockstep and a majority vote of the outputs masks any possible single CPU fault. The memory and communication subsystem faults can be masked employing ECC techniques. Its unique capability of masking any single fault, at the cost of an additional CPU, it offers a 100% error detection coverage within a single clock period. It is possible to "see" the TMR as operating in degraded mode when it is working with just two healthy CPUs [4].

#### 2.5.1.2 Dual Modular Redundancy

Figure 2-5: Triple modular redundancy (TMR or TCLS) implementation

In dual modular redundancy the configuration is quite different from the previously addressed one. In this case there is no democracy, there is no majority, just the concept of right and wrong values. As it can be seen in Figure 2-4 the outputs produced by both cores are feeding a checker unit which is responsible for identifying the inconsistencies if they appear. If such a scenario occurs it means that the system is facing some kind of fault and if not treated as soon as possible it can propagate to an error and consequently to a failure as seen in section 2.3.2.1. The disadvantage of this implementation is that it does not permit to identify which was the erroneous CPU core so if one is under fault, the system is faulty and must recover. In this implementation there is no fail degraded mode.

#### 2.5.2 Error Recover Techniques

In this phase, depending on the outcome of BIST (Built in Self Test), some action for recovery or containing the error are taken. In the DMR, if a hard error has occurred, the processors are stopped, a fatal error is signalized, and recovering the system from it is impossible. So, the system stops working and switches to a safe state. When a hard error occurs in a system with Multiple Modular Redundancy (MMR), the erroneous processor is disabled, and the other health processors keep their execution as

long as another error in the remain executing processors does not occur. After a error, if the MMR was composed of three redundant instances (TMR), the MMR starts working like a DMR redundant system. In the case the BIST does not detect any hard error, it means that a soft error has occurred. So, in the system with DMR technique, both processors are recovered to a state without any error, since it is unknown what the erroneous processor is. In the opposite side, in the MMR technique, the recovery is made to the erroneous processor only. The system keeps executing with the remaining health processors, and when the erroneous processors are recovered, the MMR changes to its fully functional state without having any execution interruption.

# 2.6 Conclusion

This chapter gave an overview of all the relevant topics that needed to be considered about safety and dependability. A particular emphasis was given to the fault-tolerance means definition and the importance of redundancy due to the fact that this project will take advantages of some fault-tolerance mechanisms such as lockstep.

The different types of lockstep configurations that currently exist and are relevant for this dissertations scope were also presented and may be addressed to better understand the concept. In addition to all that was mentioned the main advantages and disadvantages of each implementation were also shown.

# Chapter 3

# System Specification

After having a theoretical insight about concepts and technologies that this dissertation will focus on and having an overview of the lockstep mechanism, it is possible to define the application that it is intended to develop as well as the components that will be part of the system.

Primarily, it is important to outline the application scenario that this dissertation covers which is the calculation of an angle and possible faults that could outcome from the hardware used for that matter. However, on the long run, it is intended to have a functional generic architecture that allows the use of different applications without significant changes in its structure.

This chapter presents the design and specification of the system and its architecture, as well as all the requirements and constraints for the architecture that is intended to develop.

A general overview of the whole architecture is given, taking into consideration the technological study made in Chapter 2.

### 3.1 Use Case

As mentioned in previous sections, the aim of this dissertation is to develop an architecture that could still perform its intended function even under faults, achieving in this way the fail-operational behaviour. The goal is to keep it generic, enabling it to use in a variety of application scenarios, despite the fact that the main use case for this architecture is to be applied in safety critical applications as it is the steer-by-wire. Steer-by-wire must not allow faults to propagate into failures within the system since this could lead the car to cause serious harm for the people that are using it as well as for the surrounding environment. That is the reason why systems like this have the necessity to have its safety enhanced. Safety critical applications such as steer-by wire must have their subsystems in which they rely on (e.g. APS) with the

highest availability and reliability improving in that way the safety which is considered critical for that matter.

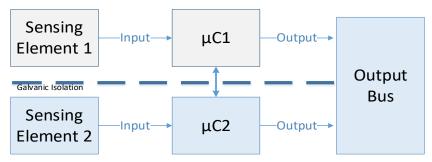

The architecture that it is intended to develop has the aim to be used on APS covering the calculation

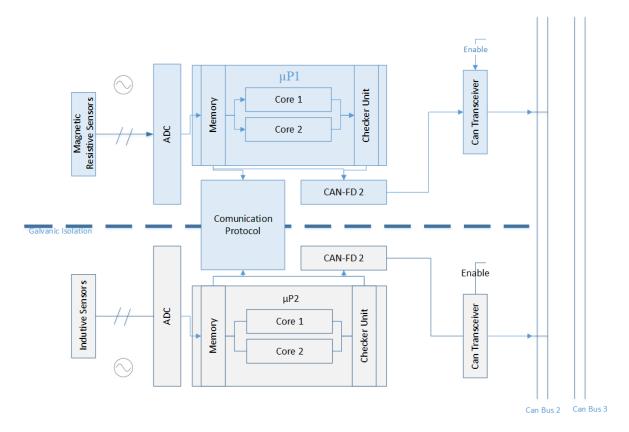

Figure 3-1: Application use case

of the angle of the steering wheel. This angle once calculated is sent to the electronic control unit (ECU) that is responsible for sending the right outputs to the actuators, the motor that controls the movement of car wheels. It can be imagined that if the subsystem responsible for calculating the angle fails, or even the actuator subsystem, all the steering system would consequently fail too. This, due to the fact that the entire steering system depends on its subsystems and there is no redundancy ensured, as it would be if the steering system was conventional (mechanic redundancy ensured by the steering column). In the conventional steering system, if APS would have failed the steering column would ensure the intention of the driver. Since this column links the steering wheel to the axis, the intention would still be transmitted to the car wheels, despite having some functionalities that would not be available anymore such as steering assistance. In order to solve the problem, which is the elimination of the steering column, the architecture that is going to be developed to perform the calculation of the angle of the steering wheel, is going to have the redundancy necessary to ensure the function even when faults occur. An overview of the architecture is shown in Figure 3-1.

# 3.2 System Requirements

To properly design an architecture, first, all of its requirements and constraints must be defined beforehand, as it is crucial to fulfil them in the decision-making process as well as in the implementation process. With that being said, Table 3-1 is presented. It describes all the conditions that the architecture must comply with to have the system fail operational as it is intended. It is important to note that some concepts addressed at the table are extremely correlated with the theoretical background approached in Chapter 2. The table is divided into 5 sections. First, the requirements are addressed in a general view of the architecture. That being comprehended and having defined what the subsystem is, then the requirements related with the subsystem are pointed out. As addressed throughout this document,

redundancy is necessary thus, redundancy for the software and hardware were also described in the table. Finally, the requirements for the subsystem communication are shown.

| ID                                                                  | Description                                                                       |  |  |  |  |  |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1. Architecture                                                     |                                                                                   |  |  |  |  |  |  |

| 1.1.                                                                | The architecture in order to achieve a fail operational behaviour shall have      |  |  |  |  |  |  |

|                                                                     | redundancy, both at software and hardware level.                                  |  |  |  |  |  |  |

| 1.2.                                                                | 1.2. The redundant hardware used, which define a subsystem, shall have galva      |  |  |  |  |  |  |

|                                                                     | isolation between them.                                                           |  |  |  |  |  |  |

| 1.3.                                                                | The architecture shall be compliant with ASIL D classification.                   |  |  |  |  |  |  |

| 1.4.                                                                | Each subsystem shall be able to communicate to the outer system using CAN/CAN-FD. |  |  |  |  |  |  |

| 1.5.                                                                | A CAN message shall be sent within a fix period of 10 milliseconds.               |  |  |  |  |  |  |

|                                                                     | 2. Subsystem                                                                      |  |  |  |  |  |  |

| 2.1.                                                                | Each subsystem shall have fault-tolerant mechanisms.                              |  |  |  |  |  |  |

| 2.2.                                                                | Each subsystem shall have a communication protocol to exchange data               |  |  |  |  |  |  |

|                                                                     | between themselves.                                                               |  |  |  |  |  |  |

| 2.3.                                                                | The microcontrollers used in each subsystem shall have an ASIL D                  |  |  |  |  |  |  |

|                                                                     | classification.                                                                   |  |  |  |  |  |  |

|                                                                     | 3. Redundant Hardware                                                             |  |  |  |  |  |  |

| 3.1.                                                                | Two processing units defining the subsystems shall compose the architecture.      |  |  |  |  |  |  |

| 3.2.                                                                | The signals acquired by both processing units shall have different sources.       |  |  |  |  |  |  |

| 3.3.                                                                | Each subsystem shall have lockstep mechanism in it.                               |  |  |  |  |  |  |

|                                                                     | 4. Redundant Software                                                             |  |  |  |  |  |  |

| 4.1.                                                                | The software developed shall take advantageous of homogeneous redundancy.         |  |  |  |  |  |  |

| 4.2.                                                                | The software developed should be able to fit in AUTOSAR architecture.             |  |  |  |  |  |  |

| 4.3.                                                                | The software shall be developed according with V-model of ISO 26262               |  |  |  |  |  |  |

|                                                                     | 5. Subsystem communication                                                        |  |  |  |  |  |  |

| 5.1.                                                                | The communication protocol that will be used for communication between            |  |  |  |  |  |  |

|                                                                     | subsystems shall be automotive certified                                          |  |  |  |  |  |  |

| 5.2. The communication protocol that will be used for communication |                                                                                   |  |  |  |  |  |  |

|                                                                     | Microcontrollers shall work with Galvanic Isolation Scenarios                     |  |  |  |  |  |  |

| 5.3.                                                                | The communication protocol that will be used for communication between            |  |  |  |  |  |  |

|                                                                     | Microcontrollers shall have multi master                                          |  |  |  |  |  |  |

| 5.4.                                                                | The communication protocol that will be used for communication between            |  |  |  |  |  |  |

|                                                                     | Microcontrollers shall have error correction codes implemented in order to        |  |  |  |  |  |  |

|                                                                     | identify faults                                                                   |  |  |  |  |  |  |

## 3.3 System Architecture

As mentioned in the previous sections, the aim of this dissertation is to develop a fail-operational architecture that still provides its supposed function, even when facing fault. Taking into account all the requirements described in 3.1 and the study presented in Chapter 2 it is possible, at this phase, to define the architecture as well as its components. For better understanding, Figure 3-2 can be referred. It depicts the full system stack containing all the different layers division between hardware and software as the elements that compose those layers.

CAN Application Error channels Software Configuration Configuration Configuration Components Event handler State Machine Timer driver GPIO driver CAN driver TIMER **FCCU EIM ERM** CAN-FD

The hardware layer contains the modules that are present in microcontroller unit (MCU) and were

Figure 3-2: System Stack

used for the purpose of the project and of course the MCU. Below this MCU layer the CAN physical layer needed to have the communication performed is presented. All the other modules present in hardware layer are used for both communication and diagnosis purposes.

The software layer contains the modules needed to be developed for the good functioning of this architecture. All the software that is developed followed the guidelines demanded by the AUTOSAR architecture. AUTOSAR architecture is a standard created in consortium of automotive companies to standardize the software developed by those companies. In the MCAL layer all the drivers responsible for managing directly over the hardware are presented. Some of those drivers, such as CAN-FD, were already developed and for this project were only used from an user point of view. At the ECUAL there is no module represented since no module that fits in this layer was developed. Either way, this layer

intended to act like an interface between the upper layers and the MCAL. In this project the communication between the upper layers and the MCAL are going to be made through Service Layer, with exception of CAN-FD module that uses the ECUAL as an interface. Most of the modules of this project are going to be used for diagnostic purposes so it makes more sense to organise the software in that way. At the service layer there is going to be placed the state machine that is intended to be designed to keep the system under control as the event handler. This last one will be the module responsible to react to faults when they occur. In the upper layer, there is all the software responsible for the application. This layer is composed mostly of configurations made at the higher level where the amount of channels that are going to be used to report the errors are defined; CAN-FD channels and initiating all the modules necessary for the project. It is also at this level that the software components are present for the use case application. Nevertheless, for the purpose of this dissertation they are not going to be developed despite being referenced later in implementation to depict how the software will interact.

# 3.4 Hardware Specification

Having the system requirements and system architecture addressed is now time to go deep into the hardware level. This section intends to describe hardware components that this Master's Thesis will focus on. Considering that at the hardware level is represented essentially by the MCU, and MCU's peripherals, this section will have a top-down approach. First the microcontroller will be addressed followed by MCU's peripherals.

#### 3.4.1 Microcontroller

As stated in 3.1, for each microcontroller used in this system's scope lockstep must be included. With that constraint, the choice of a microcontroller turned out to be very limited. The market does not have a wide choice when it comes to a microcontroller that has lockstep mechanisms certified for the automotive. For that reason and after some negotiations with NXP semiconductors the chosen microcontroller is a S32K2TV. This microcontroller is an evaluation board that NXP provides for the

purpose of this dissertation. It is believed that this board will not be released in the market. However, some variants of it will.

Figure 3-3: S32K2TV Board

The lockstep that this board has, is based in DMR. Said that, and since it is needed to have two cores for fulfilling this feature, the cores that are being used with that purpose are two ARM Cortex M33. These processors are massively used in safety critical applications due to its security specifications and high-performance modules that it has, such as, trust-zone memory, Digital Signal Processing (DSP) and, Floating Point Unit (FPU). Nevertheless, the M33 processors that this board has included in do does not have a trust-zone memory. In S32K2TV as it was said previously, there are two cores running in two-cycle delayed lockstep, meaning, the operation that one core is performing will be executed on the second one with two clock cycles delay.

Figure 3-4: MCU's Lockstep