### Universidade do Minho

Escola de Engenharia

José Miguel Penteado Neiva Silva Fernandes

Design, fabrication and integration of 3D micro-structures using self-folding techniques for ultra-miniaturization of smart microsystems

Design, fabrication and integration of 3D micro-structures using sel

Minho 12019

#### Universidade do Minho

Escola de Engenharia

José Miguel Penteado Neiva Silva Fernandes

Design, fabrication and integration of 3D micro-structures using self-folding techniques for ultra-miniaturization of smart microsystems

Tese de Doutoramento em Engenharia Biomédica

Trabalho efetuado sob a orientação do **Professor Doutor Paulo Mateus Mendes** e do

**Professor Doutor Luís Alexandre Rocha**

#### Direitos de autor e condições de utilização do trabalho por terceiros

Este é um trabalho académico que pode ser utilizado por terceiros desde que respeitadas as regras e boas práticas internacionalmente aceites, no que concerne aos direitos de autor e direitos conexos. Assim, o presente trabalho pode ser utilizado nos termos previstos na licença abaixo indicada. Caso o utilizador necessite de permissão para poder fazer um uso do trabalho em condições não previstas no licenciamento indicado, deverá contactar o autor, através do RepositóriUM da Universidade do Minho.

#### Licença concedida aos utilizadores deste trabalho

Atribuição

CC BY

https://creativecommons.org/licenses/by/4.0/

## **Acknowledgments**

First, I would like to thank my family, for all the support through all my academic research path. Without them, nothing would be possible, and with their strength and persistence. I was able to get here and finish my PhD. José, Margarida and Ana, for all these years I hope I've matched your expectations and "thank you" both for this opportunity. Rita, my girlfriend, thank you for all the patience and company during this complex process. Your unconditional love made me a better person, thank you for being with me all the time and helping me achieve most of my accomplishments. Thank you for making me smile every day. To my supervisors I would like to thank all the effort and the patience to get me here. Because of your enthusiasm and your strength, Prof. Paulo Mendes, now I know the importance of "integration" and how to believe in my own work. Thank you for not letting me give up on this dream and staying strong during the process. For Prof. Luis Rocha, thank you for all. You brought me to INL and gave me one big opportunity for my life. Without you my PhD would not be possible. I will always miss you. To my previous lab colleagues, I want to acknowledge your effort to make me laugh, smile and proceeded with this complicated work without giving up. A really special thanks to Hugo and Anacleto for helping me putting it all together and for being a great friends through these years. Another special thanks for the guys who took the same course and same the PhD as me, Ginho and Cocas. I'm happy to have you both as close friends. In INL, a special thanks to all my coworkers, João, Helder, José, Mariana, Bernardo, Joana, Eurico and Filipe. You gave me training, opportunities and most of the knowledge to do this PhD. I'm profoundly happy to have you now by my side every day. Diogo a special thanks to you, for losing your precious time correcting this thesis. To João Gaspar, a really big thank you for being my friend, helping me with everything, and giving me the most wonderful opportunity of my life.

The author, José Miguel Fernandes, was supported by the Portuguese Foundation for Science and Technology (Programa Operacional Temático Fatores de Competitividade COMPETE), and by INL (Iberian Nanotechnology Laboratory) Grant: SFRH/BD/100649/2014 FCT; PTDC/EEI-TEL/5250/2014; Fundo Comunitário Europeu, FEDER and the National Science Foundation, POCI-01-145-FEDER-16695.

#### STATEMENT OF INTEGRITY

| I hereby declare having conducted my thesis with integrity. I confirm that I have not used plagiarism    |

|----------------------------------------------------------------------------------------------------------|

| or any form of falsification of results in the process of the thesis elaboration.                        |

| I further declare that I have fully acknowledged the code of ethical conduct of the University of Minho. |

|                                                                                                          |

|                                                                                                          |

|                                                                                                          |

| University of Minho,                                                                                     |

| José Miguel Penteado Neiva Silva Fernandes                                                               |

| Signatura:                                                                                               |

#### Resumo

Devido aos avanços recentes na área das microtecnologias, são cada vez menores as dimensões dos microdispositivos o que permite a sua utilização em aplicações até aqui impossíveis. Surgem assim, cada vez mais os dispositivos médicos implantáveis com potencial para introduzir benefícios significativos no âmbito do diagnóstico e do tratamento localizado. A integração de tais dispositivos é assim um processo muito complexo pois estes precisam de ser pequenos e biocompatíveis. Para tal, novas tecnologias de integração são atualmente investigadas para conseguir transformar projetos de investigação em produtos que podem ser produzidos em grandes quantidades em centros microfabricação. Na investigação, a integração manual de diferentes dispositivos é muito comum, dificultando muitas vezes o processo fabrico e a própria funcionalidade do dispositivo. Consequentemente, muitos projetos de investigação não avançam para a produção e o dispositivo nunca chega a ser utilizado para o fim que foi desenvolvido. A integração é então, um processo fundamental que afeta não só a funcionalidade do dispositivo mas também o seu processo de fabrico. Para tal, esta integração deve ser considerada desde o início de cada projeto para facilitar a escalabilidade do produto final.

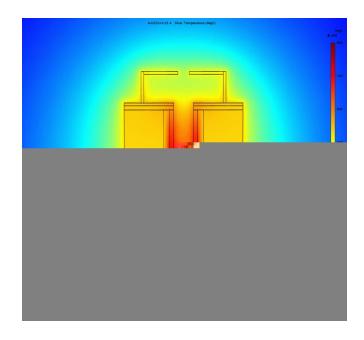

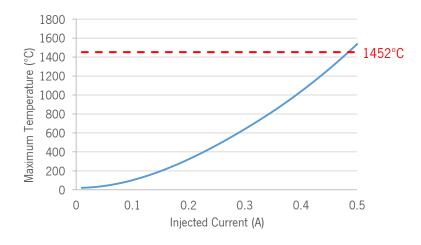

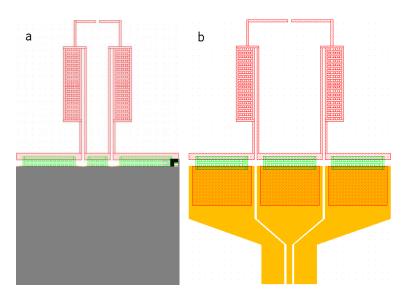

Esta tese foca-se neste problema e teve como objetivo a criação de um processo novo para integrar estruturas 3D com substratos de silício. Utilizando apenas este processo a integração de sensores e atuadores complexos com os seus circuitos de controlo e gestão de energia é uma realidade. Este processo é obtido através da combinação de diferentes técnicas de fabrico de sala limpa. Utilizando técnicas comuns promove-se assim a escalabilidade do processo. Para obter tais estruturas o processo passa por três litografias e três eletrodeposições, seguidas de um processo de self-folding que converte padrões 2D em estruturas 3D. Para prova de conceito, um micro atuador 3D foi desenhado e simulado. A simulação elétrica, mecânica e térmica foi realizada para perceber todo o funcionamento do dispositivo. Após fabricação os resultados simulados são semelhantes aos resultados medidos. O micro atuador fora do plano foi fabricado em cima de um substrato de silício como requerido, permitindo assim que estes dispositivos sejam facilmente integrados com outros sistemas complexos. O objetivo desta tese foi concluído com sucesso e a sua principal contribuição foi a criação de um processo complexo para integrar estruturas 3D em cima de substratos de silício utilizando apenas técnicas padrão de sala limpa.

Palavras-Chave: Integração; Microfabricação; Self-Folding; Estruturas Tri-dimensionais.

Design, fabrication and integration of 3D micro-structures using self-folding techniques for ultraminiaturization of smart microsystems

**Abstract**

Recent advances in micro technology, are delivering complex devices that can measure and

actuate in places that were thought unreachable. Implantable devices are a reality that will bring forth

great, new opportunities in medical field, both in treatment and diagnostics. Such devices are required

to be as small as possible, creating the necessity for new complex integration technologies that can be

used in the industry. In research, the handmade ad hoc integration of different devices and different

systems is quite common. When these very small devices need some reproducibility to be implemented

at an industrial scale, such methodology does not work properly. Integration has, in fact, an important

role in today's creations, because it will affect the device volume, characteristics, performance and its

own fabrication process. In this way, the integration process should be considered a part of full devices'

development process, since it will ultimately limit the achievable features.

This thesis addresses this problem and creates a new integration process to fabricate and

attach 3D structures on silicon wafers. Such fabrication technology allows the integration of complex

3D sensors and actuators with their control circuitry and power management in a single process. The

fabrication process gathered a lot of different cleanroom standard techniques that allow the scalability

of the process into big fabrication centres. Three lithographies followed by three electrodepositions

gave way to the device, and a new technology called self-folding, transforms the 2D patterns in 3D

complex structures. For proof of concept, an out-of-plane 3D antennas and a micro actuator were

designed and fabricated within this PhD. At last, the 3D actuator electrical, mechanical and thermal

simulations were compared with the measurement results, leading to a very good match between

them.

After the fabrication process, the micro actuator is out-of-plane on top of a silicon substrate, as

intended. With such fabrication process, these devices can be easily tested and used in complex

systems. The main objective of this thesis was achieved with success, delivering its main contribution:

a complex process to integrate 3D structures on top of silicon substrates using only standard cleanroom

techniques.

**Keywords**: Integration; Microfabriaction; Self-Folding; Three-dimensional Structures.

## **Table of Contents**

| CHAPTER 1. | INTRODUCTION                                           | 1  |

|------------|--------------------------------------------------------|----|

| 1.1. Imp   | antable devices                                        | 1  |

| 1.2. Thei  | mal modulation microdevices                            | 4  |

| 1.3. Integ | gration and miniaturization technologies               | 6  |

| 1.3.1.     | 2D and 2.5D Integration technologies                   | 8  |

| 1.3.2.     | 3D Integration technologies                            | 10 |

| 1.3.3.     | Multiple integration technologies                      | 12 |

| 1.3.4.     | Non-conventional integration technologies              | 13 |

| 1.4. Obje  | ctives and contributions                               | 13 |

| 1.4.1.     | List of publications                                   | 16 |

| CHAPTER 2. | FABRICATION TECHNOLOGIES AND PROCESSES                 | 18 |

| 2.1. Clea  | nroom and facilities                                   | 18 |

| 2.2. 3D S  | Structuring technologies – Fabrication and integration | 18 |

| 2.2.1.     | Sub-micron 3D printing                                 | 19 |

| 2.2.2.     | Micro direct writing laser technologies                | 21 |

| 2.2.3.     | Cleanroom technologies                                 | 23 |

| 2.2.4.     | Fabrication processes overview                         | 25 |

| 2.3. Self- | Folding                                                | 26 |

| 2.3.1.     | Surface tension driven folding                         | 26 |

| 2.3.2.     | Self-Folding in aqueous medium                         | 28 |

| CHAPTER 3. | 3D INTEGRATION DEVELOPMENT                             | 31 |

| 3.1. Ultra | a-Small packaged micro-cooler                          | 31 |

| 3.1.1.     | Pre-packaging steps                                    | 32 |

| 3.1.2.     | Packaging process flow                                 | 33 |

| 3.2. Elec  | trodeposition setup development                        | 37 |

| 3.2.1.     | Nickel electrodeposition system                        | 39 |

| 3.2.2.     | Electroplating setup calibration                       | 43 |

| 3.2.3.     | Tin electrodeposition system                           | 46 |

| 3.3. Self- | Folding process development at INL                     | 49 |

| 3.3.1.     | Mask preparation                                       | 49 |

| 3.3.2.     | Standard cleanroom processing                          | 52 |

| 3.3.3.     | Electrodeposition                                      | 57 |

| 3.3.4.     | Removal of the sacrificial layers                      | 60 |

| 3.3.5.     | 3D Folding                                             | 62 |

| 3.4. Con   | clusion and process comparison                         | 63 |

| CHAPTER 4. | INTEGRATION CASE STUDIES                               | 65 |

| 4.1. The   | mally actuated micro tweezers                          | 65 |

| 4.1.1.     | Displacement analysis                                  | 72 |

| 412        | Device resistance analysis                             | 73 |

| 4.1.    | 3. Stress analysis                              | 74  |

|---------|-------------------------------------------------|-----|

| 4.1.    | 4. Temperature analysis                         | 76  |

| 4.1.    | 5. Final device analysis and design             | 77  |

| 4.2.    | 3D On-wafer antennas                            | 79  |

| 4.2.    | 1. 60 GHz Small cubic antenna                   | 79  |

| 4.2.    | 2. 36 GHz Small dipole antenna                  | 81  |

| CHAPTE  | R 5. EXPERIMENTAL RESULTS                       | 83  |

| 5.1.    | Anchored self-Folding process                   |     |

| 5.2.    | Anchored process flow                           |     |

| 5.2.    |                                                 |     |

| 5.2.    |                                                 |     |

| 5.2.    | - 7                                             |     |

| 5.2.    |                                                 |     |

| 5.2.    | 5 1 7                                           |     |

| 5.2.    | 1 0                                             |     |

| 5.2.    | 1 3                                             |     |

| 5.2.    | , ,                                             |     |

| 5.2.    | 5                                               |     |

| 5.3.    | Micro Tweezer functional measurements           |     |

| 5.3.    | ·                                               |     |

| 5.3.    |                                                 |     |

| 5.3.    |                                                 |     |

| CHAPTE  |                                                 |     |

| 6.1.    | Conclusions                                     |     |

| 6.2.    | Future work                                     |     |

| 6.2.    | 5                                               |     |

| 6.2.    | 2. Innovative three-dimensional routing         | 115 |

| REFEREI | ICES                                            | 117 |

| APPEND  | X                                               | 122 |

| Appen   | dix 1. Fabrication Technologies                 | 122 |

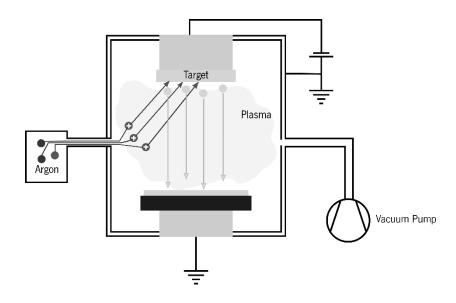

| a.      | Sputtering Deposition                           |     |

| b.      | Chemical Vapour Deposition                      |     |

| C.      | Optical Lithography                             |     |

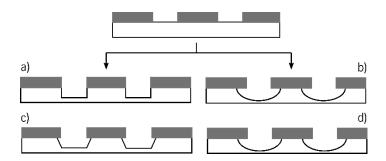

| d.      | Chemical Etch                                   |     |

| e.      | Dicing                                          |     |

| f.      | Metrology                                       |     |

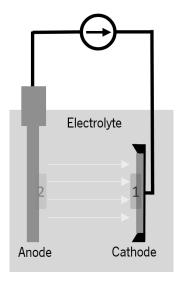

| g.      | Electrodeposition                               |     |

| Appen   | ·                                               |     |

| a.      | Electrodeposition solutions                     |     |

| b.      | Materials selection                             |     |

| C       | Nickel electrodeposition chemical compatibility | 143 |

| d.   | Tin electrodeposition chemical compatibility                               | 145 |

|------|----------------------------------------------------------------------------|-----|

| e.   | Nickel electrodeposition system – Cylindrical Approach                     | 146 |

| f.   | Tin electrodeposition system – Rectangular Approach                        | 151 |

| Appe | ndix 3. Recipes of different techniques                                    | 157 |

| a.   | Al2O3 Deposition – Timaris FTM                                             | 157 |

| b.   | Adhesion and Seed Layer Deposition - Kenosystec                            | 157 |

| c.   | a-Si CVD Deposition – SPTS PECVD                                           | 157 |

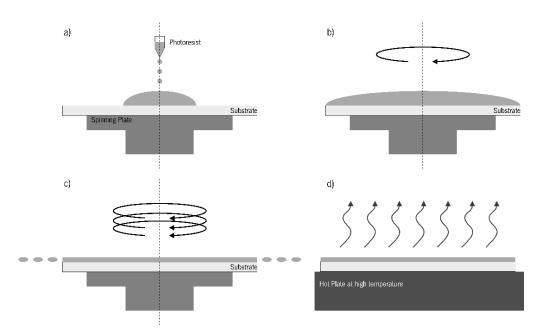

| d.   | First Lithography – SUSS Gama Cluster + SUSS Mask Aligner MA6B6            | 158 |

| e.   | a-Si etching – SPTS Pegasus                                                | 158 |

| f.   | Second and Third Lithography - SUSS Gama Cluster + SUSS Mask Aligner MA6B6 | 159 |

| Appe | ndix 4. Runsheets                                                          | 161 |

| a.   | Mask Runsheet at INL Cleanroom                                             | 161 |

| b.   | Runsheet used in INL Cleanroom on the last process                         | 165 |

# **Index of Figures**

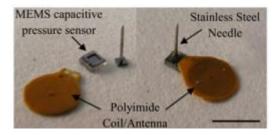

| Figure 1.1. IOP measurement system, disassembled and assembled (Adapted from [4])                                                                                                                                                                                                                                                                                                                                                              | 2               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

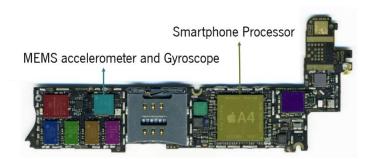

| Figure 1.2. Smartphone logic board where different devices can be seen (Adapted from [38])                                                                                                                                                                                                                                                                                                                                                     | 7               |

| Figure 1.3. 2D Integration of a complex accelerometer developed by: Colibrys Ltd [34].                                                                                                                                                                                                                                                                                                                                                         | 8               |

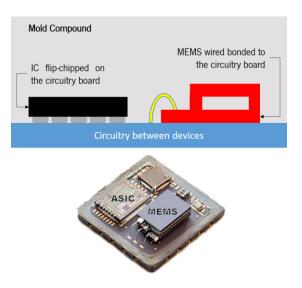

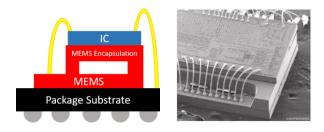

| Figure 1.4. 2D Chip level integration of the MEMS and IC [34]                                                                                                                                                                                                                                                                                                                                                                                  | 9               |

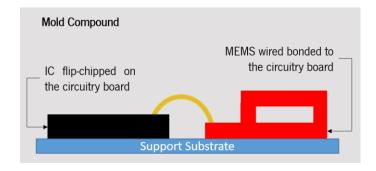

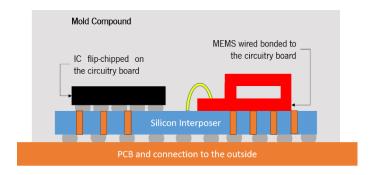

| Figure 1.5. 2.5D Integration of a device and an IC with a silicon interposer as described in [40]                                                                                                                                                                                                                                                                                                                                              | 10              |

| Figure 1.6. 3D Wafer Level Integration of a device and an IC as described in [41].                                                                                                                                                                                                                                                                                                                                                             |                 |

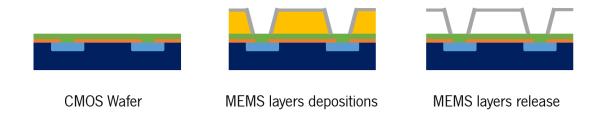

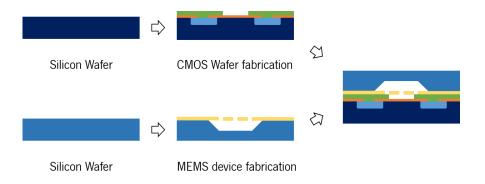

| Figure 1.7. 3D Wafer Level Integration of a device and an IC as described in [42]                                                                                                                                                                                                                                                                                                                                                              | 11              |

| Figure 1.8. STMicroelectronics accelerometer package as described in [34]                                                                                                                                                                                                                                                                                                                                                                      | 12              |

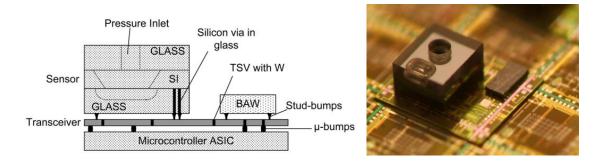

| Figure 1.9. Complex autonomous pressure sensor as described in [44]                                                                                                                                                                                                                                                                                                                                                                            | 12              |

| Figure 1.10. Complex integrated device with several MEMS described in [45].                                                                                                                                                                                                                                                                                                                                                                    | 13              |

| Figure 1.11. Project work flow for building a full integrated microdevice. Highlighted in red, the objectives                                                                                                                                                                                                                                                                                                                                  | of this         |

| work                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14              |

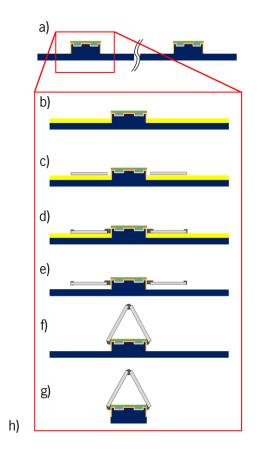

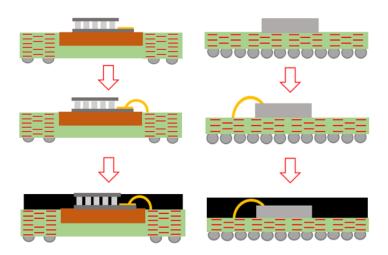

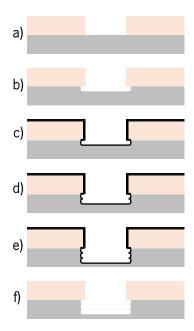

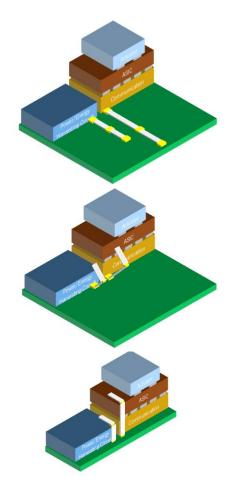

| Figure 1.12. Wafer-level packaging: a) CMOS wafer processed in a foundry; b) Deposition of a sacrificial laperosition of the main plates of the MEMS device; d) Deposition of the hinges of the MEMS device; e) Report the sacrificial layer by etching processes; f) Folded device integrated with the ASIC; g) Dicing of the full now integrated with the complex device; h) Final devices produced with the proposed wafer-level packaging. | moval<br>wafer, |

| process.                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

| Figure 2.1. Inkjet printing of a 3D antenna (Adapted from [51]).                                                                                                                                                                                                                                                                                                                                                                               |                 |

| Figure 2.2. 3D structures fabricated with commercially available SL machines (Adapted from [53], [54]).                                                                                                                                                                                                                                                                                                                                        |                 |

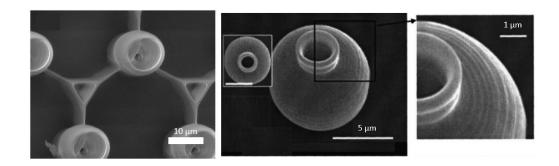

| Figure 2.3. 2PP micro structures (Adapted from [55], [58]).                                                                                                                                                                                                                                                                                                                                                                                    |                 |

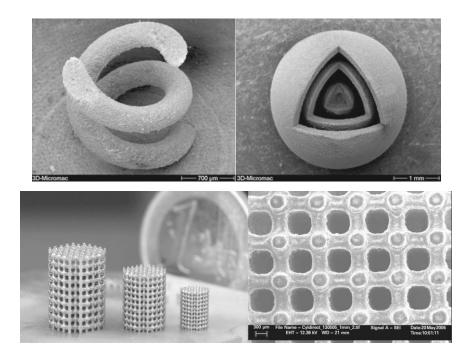

| Figure 2.4. Metallic structures fabricated with selective laser sintering (Adapted from [59], [60])                                                                                                                                                                                                                                                                                                                                            |                 |

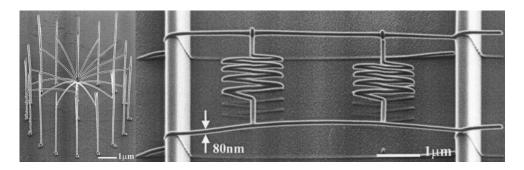

| Figure 2.5. 3D FIB structuring of small wires (Adapted from [59], [60])                                                                                                                                                                                                                                                                                                                                                                        |                 |

| Figure 2.6. LIGA process for 3D fabrication (Adapted from [64]).                                                                                                                                                                                                                                                                                                                                                                               |                 |

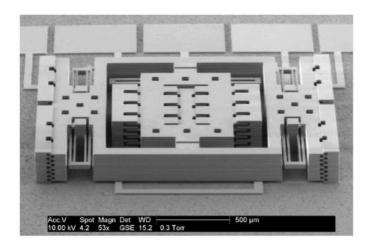

| Figure 2.7. EFAB process of a microgyroscope (Adapted from [65]).                                                                                                                                                                                                                                                                                                                                                                              |                 |

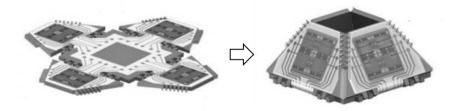

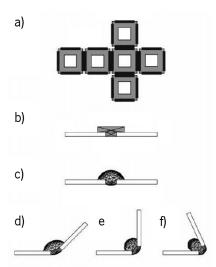

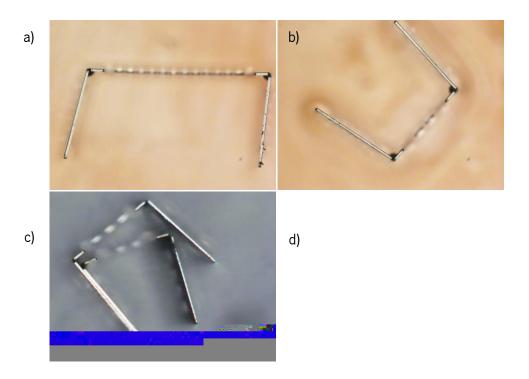

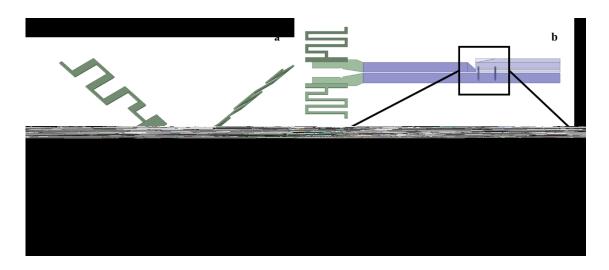

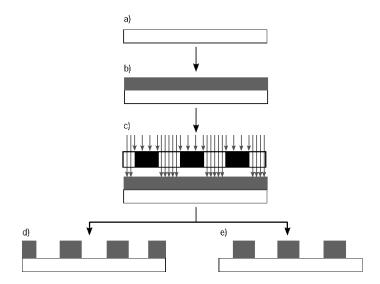

| Figure 2.8. Self-Folding Process. a) 2D planification of the sample; b) Side view of the microfabricated structure of the microfabricated structure.                                                                                                                                                                                                                                                                                           |                 |

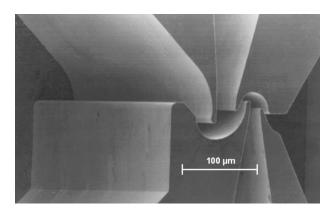

| with the panels and the hinge; c) Melted hinge after the temperature increase; d) e) and f) folding step wh                                                                                                                                                                                                                                                                                                                                    |                 |

| hinge lifts the right panel [79].                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

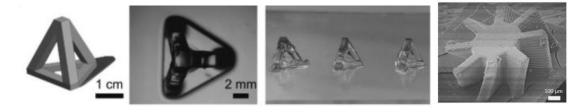

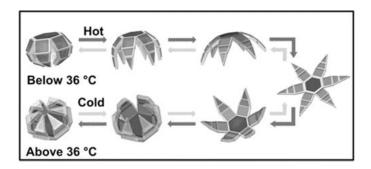

| Figure 2.9. Microgrippers developed by David Gracias laboratory [82]                                                                                                                                                                                                                                                                                                                                                                           |                 |

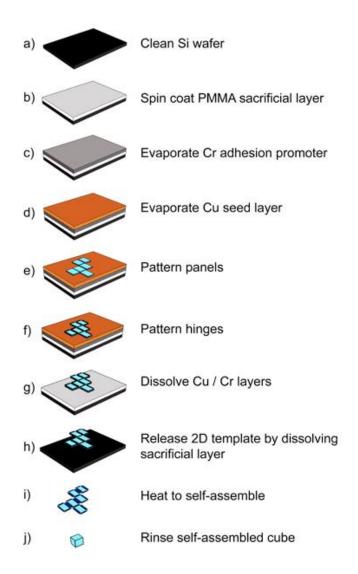

| Figure 2.10. Process flow adapted from [83]                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

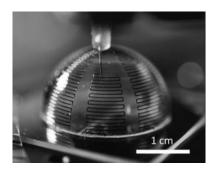

| Figure 2.11. 3D antennas developed with a self-folding technique (Adapted from [12])                                                                                                                                                                                                                                                                                                                                                           |                 |

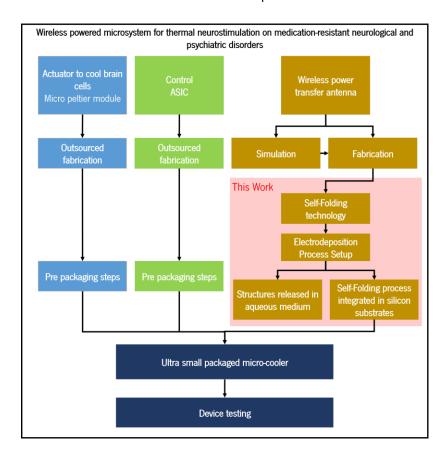

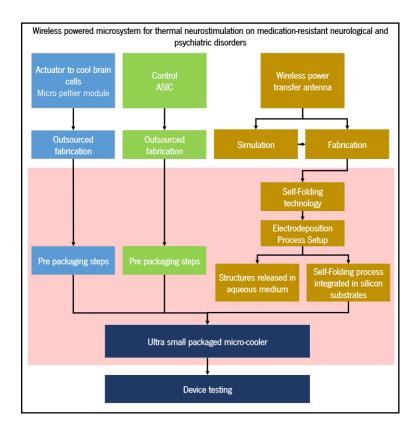

| Figure 3.1 Project diagram. In red is highlighted the area of interest that is important to take into account                                                                                                                                                                                                                                                                                                                                  |                 |

| developing a new process.                                                                                                                                                                                                                                                                                                                                                                                                                      | 32              |

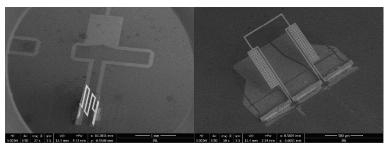

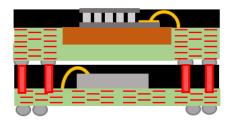

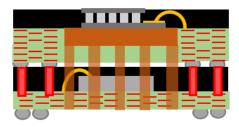

| Figure 3.2 a) ASIC designed in house to control the microsystem; b) Peltier device integrated with a heat                                                                                                                                                                                                                                                                                                                                      |                 |

| layer of Cu; c) 3D antenna required for this device                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| Figure 3.3 Integration of the chips (left: Peltier device; right: ASIC device chip) with laminate substrates a                                                                                                                                                                                                                                                                                                                                 |                 |

| corresponding wire bonding, succeeded by injection of the mold compound                                                                                                                                                                                                                                                                                                                                                                        |                 |

| Figure 3.4 Fabrication of the through-mold vias.                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| Figure 3.5 Fabrication of the thermal vias (represented in brown).                                                                                                                                                                                                                                                                                                                                                                             |                 |

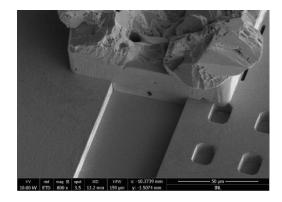

| Figure 3.6 3D self-folding antenna fabricated on top of a silicon substrate                                                                                                                                                                                                                                                                                                                                                                    |                 |

| Figure 3.7 Proposed final integrated device.                                                                                                                                                                                                                                                                                                                                                                                                   |                 |

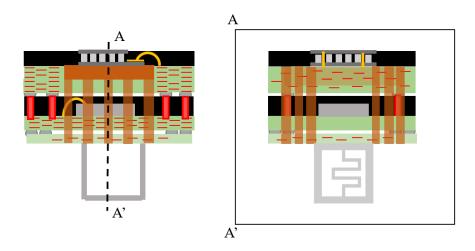

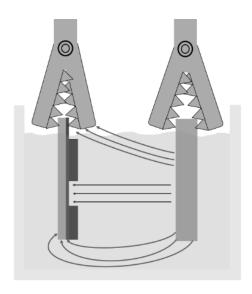

| Figure 3.8. Wafer holder; spring loaded electrical connection; section view of the electrodeposition holder:                                                                                                                                                                                                                                                                                                                                   |                 |

| wafer (light blue); electrical path (black arrows);                                                                                                                                                                                                                                                                                                                                                                                            |                 |

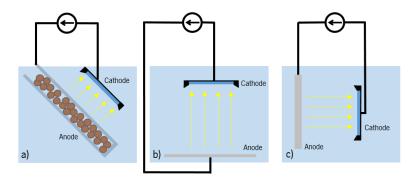

| Figure 3.9. Cathode and anode position in different electrodeposition systems. a) A.M.M.T. system for cor                                                                                                                                                                                                                                                                                                                                      |                 |

| plating; b) First version of the electrodeposition system design in this work; c) Classic electrodeposition se                                                                                                                                                                                                                                                                                                                                 | tup. 39         |

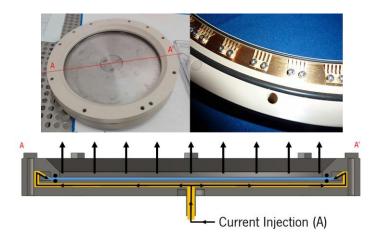

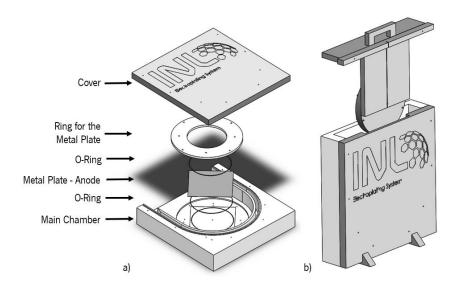

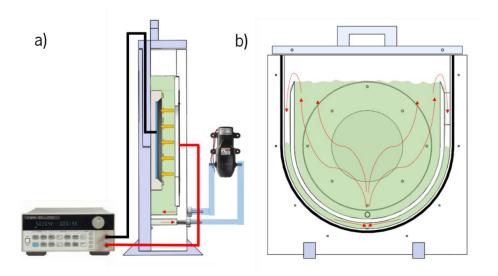

| $\label{lem:condition} Figure 3.10. Electrodeposition setup-second version. a) Deconstructed main chamber; b) Main chamber with the property of the propert$ |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| feet in final position and wafer holder attached to the wafer handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Figure 3.11. Electrodeposition setup – second version. a) Side view with the details of the electric circuit and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | the  |

| pump system; b) Front view giving the perspective of the interior of the chamber (the seal rubber is represent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| in black), the liquid flow is presented with the red arrows.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

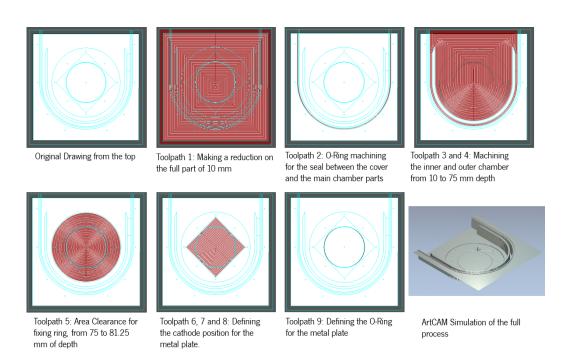

| Figure 3.12. Detailed ArtCAM process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 42 |

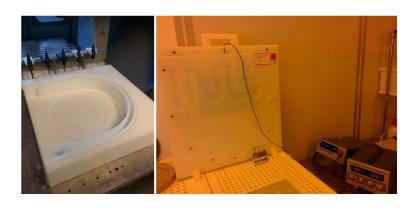

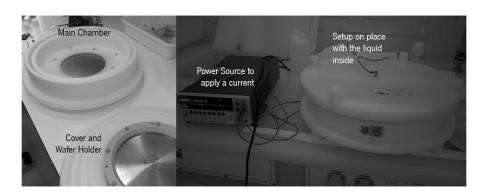

| Figure 3.13. Main chamber after milling and full system inside the cleanroom.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 42 |

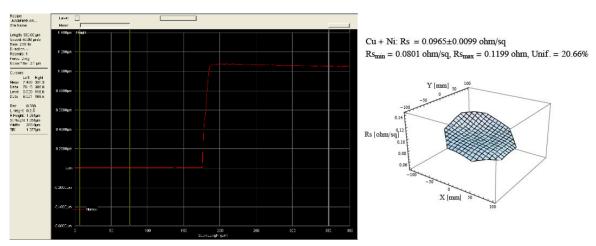

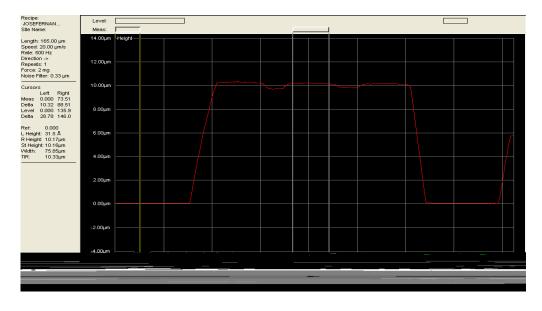

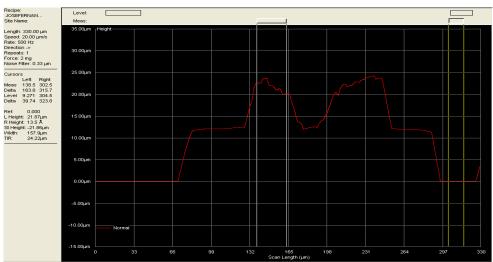

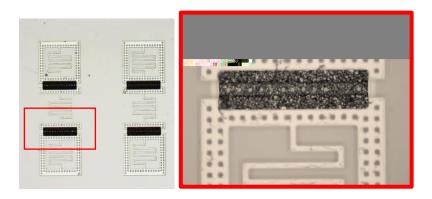

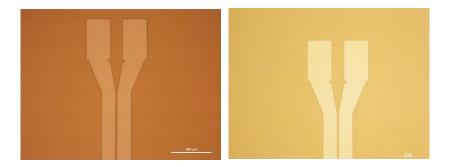

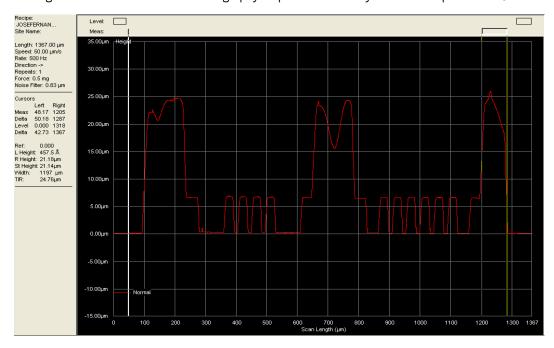

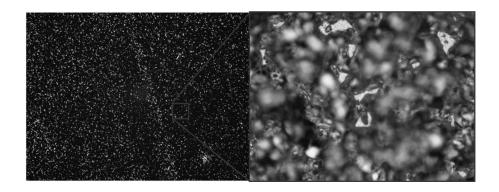

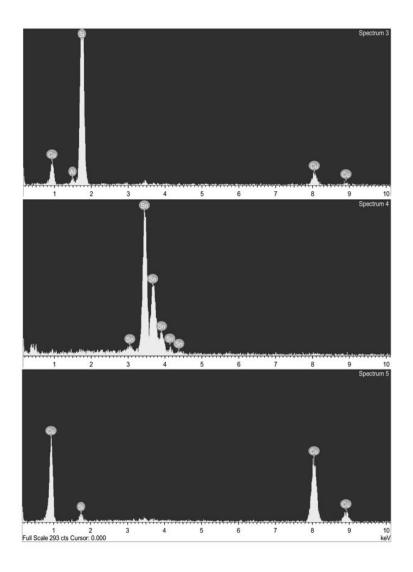

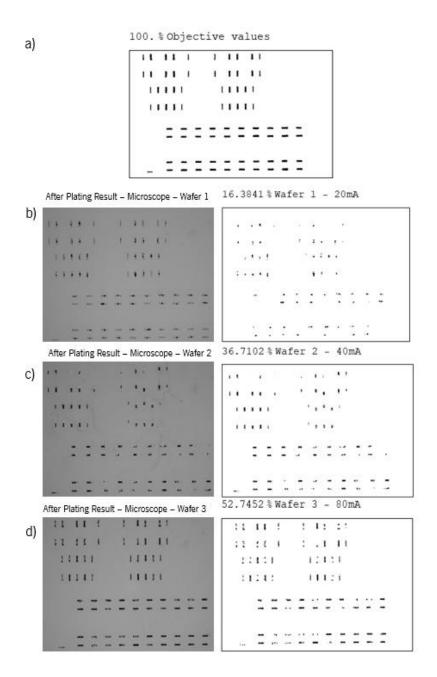

| Figure 3.14. Wafer with plated layer, sheet resistance and profilometer measurement of the thin film of Ni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 43 |

| Figure 3.15. Four point probe setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 44 |

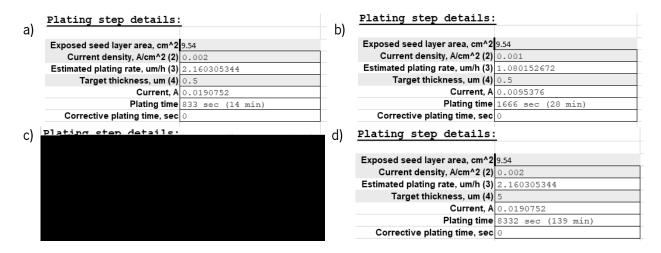

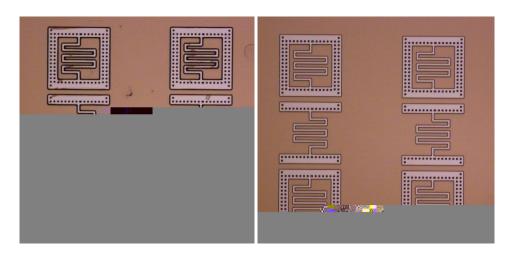

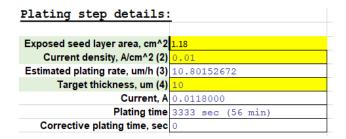

| Figure 3.16. Developed calculation sheet for the electrodeposition setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 46 |

| Figure 3.17. Tin plating setup for small samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

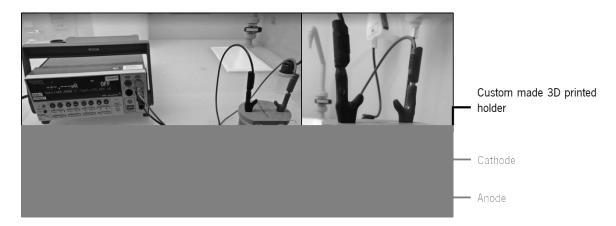

| Figure 3.18. Tin sample in a small sample setup with 1.4 mA injected between the anode and cathode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

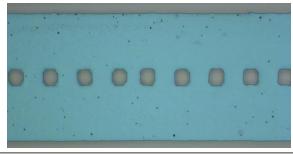

| Figure 3.19. Losses in current represented by arrows in brown, in red the electrodeposition current wanted fo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| this setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

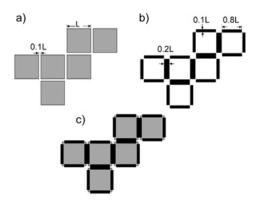

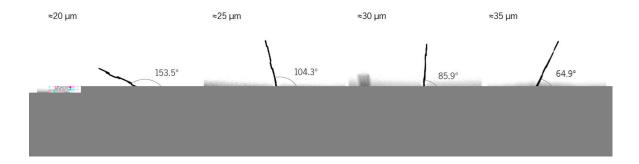

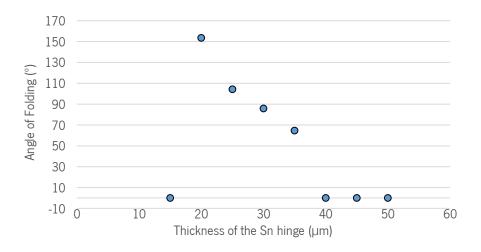

| Figure 3.20. Recommendation dimensions for a 90° folding [83]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

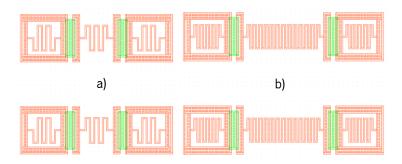

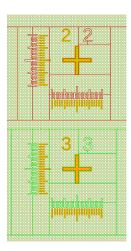

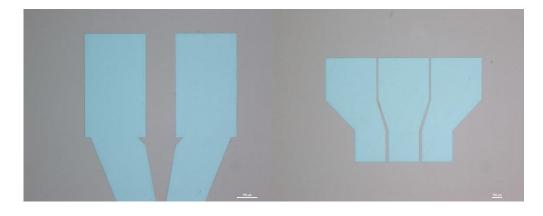

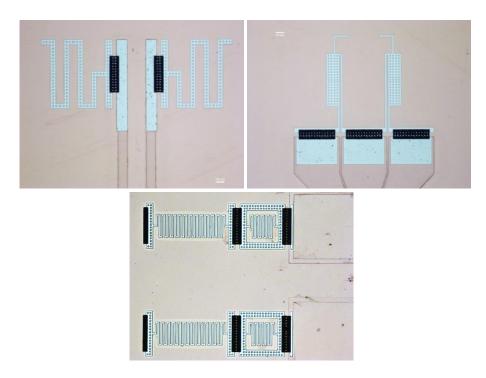

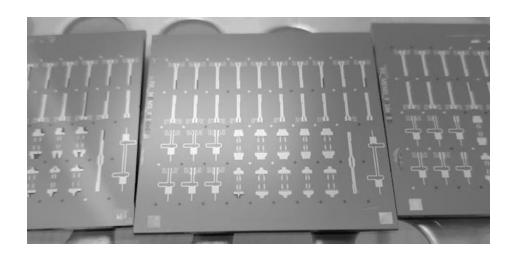

| Figure 3.21. CAD drawing of the small antennas plates (red) for mask 1, and hinges (green) for mask 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

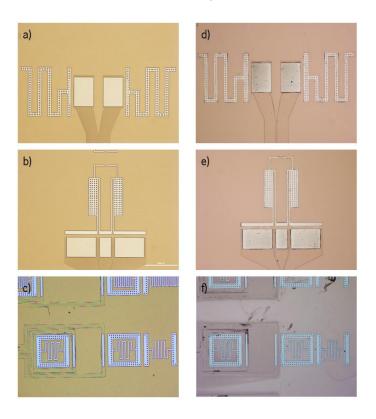

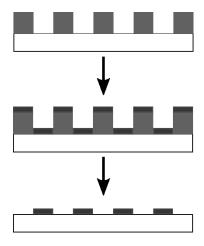

| Figure 3.22. Mask process flow.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

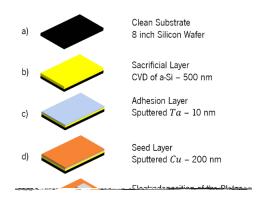

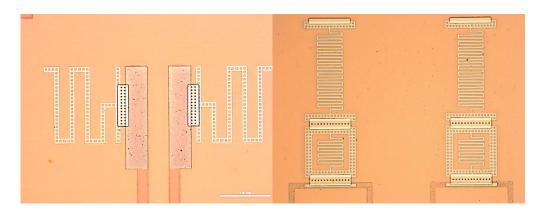

| Figure 3.23. Microfabrication process flow for 3D self-folding structures adapted to INL cleanroom.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

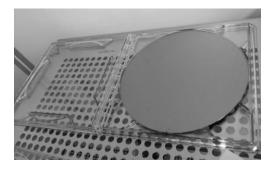

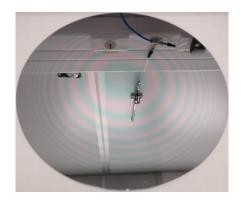

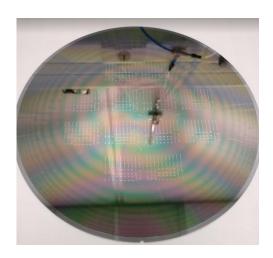

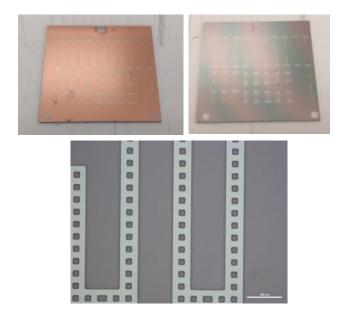

| Figure 3.24. Wafer deposited with a-Si at 150°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

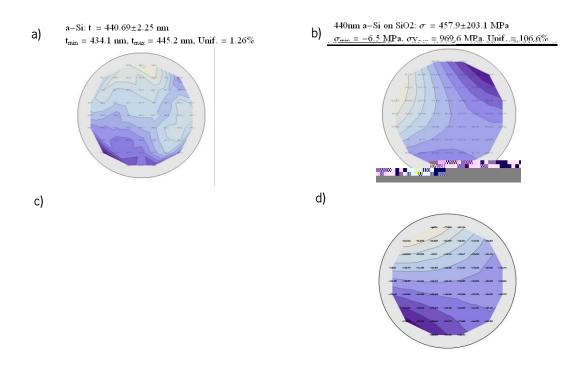

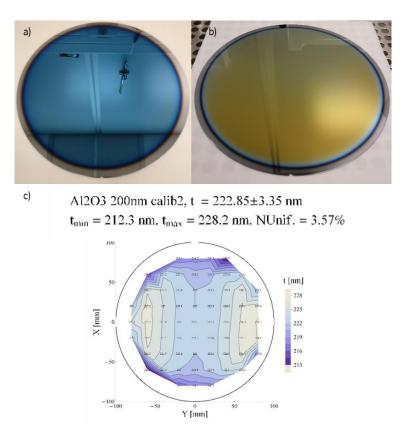

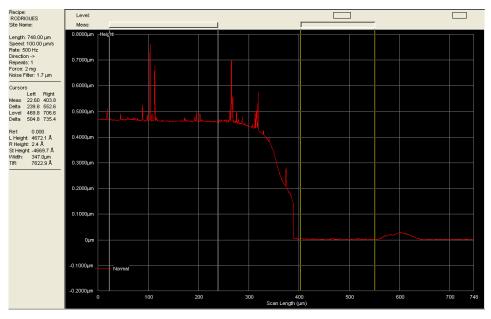

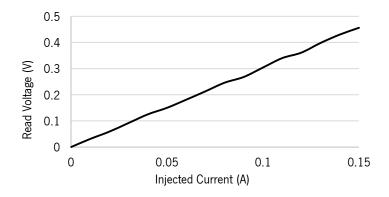

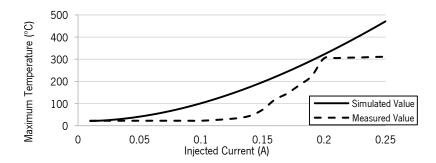

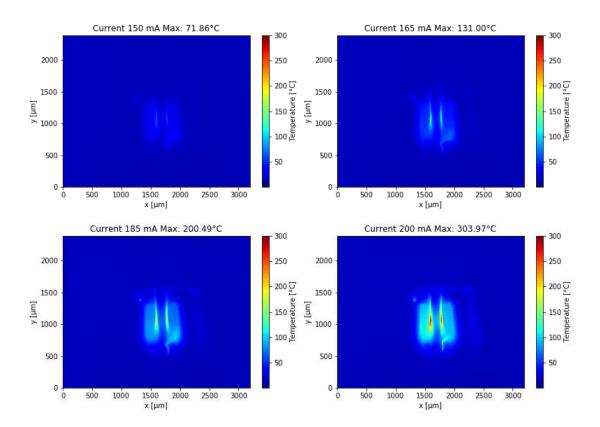

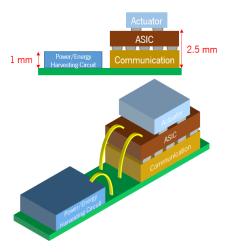

| Figure 3.25. Thickness measurements (left) and Residual stress measurements (right) of two a-Si depositions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |