Roberto Carlos Sá Ribeiro dynamic workload and power management

\*

91∩Z | ouuilMir

**Universidade do Minho** Escola de Engenharia

Roberto Carlos Sá Ribeiro

Numerical Simulations on Heterogeneous Systems: dynamic workload and power management

outubro de 2018

**Universidade do Minho** Escola de Engenharia

Roberto Carlos Sá Ribeiro

### Numerical Simulations on Heterogeneous Systems: dynamic workload and power management

Tese de Doutoramento em Informática

Trabalho efetuado sob a orientação do **Professor Doutor Luís Paulo Santos** do **Professor Doutor Miguel Nóbrega** e do **Professor Doutor Hrvoje Jasak**

### STATEMENT OF INTEGRITY

I hereby declare having conducted my thesis with integrity. I confirm that I have not used plagiarism or any form of falsification of results in the process of the thesis elaboration. I further declare that I fully acknowledged the Code of Ethical Conduct of the University of Minho.

University of Minho, 23 of October, 2018

There forall

# Acknowledgements

This thesis was not made in one day, and across the challenging days of its development, several were the people that motivated and supported me. I would like to thank my supervising team, Luís Paulo Santos (University of Minho), Miguel Nóbrega (University of Minho) and Hrvoje Jasak (University of Zagreb), for their support and knowledgeful guidance. Among these, I would like to exalt my gratitude to Luís Paulo Santos. By helping me overcoming technical issues, funding issues, motivational issues, among others, I can honestly state that the successful achievement of this work would not be possible without his support.

I also want to thank Professor Alberto Proença (University of Minho), for all the support and especially, for providing the means to pursue and achieve this thesis. I am also truly grateful to João Barbosa (TACC - University of Texas) as he was, not only a friend but also a co-worker, research partner, co-author and brainstorming partner. He was also largely responsible for my time in TACC (Texas, USA), to which I greet and extend my gratitude. Thank you to current and former members of my research group (LabCG, UM), in particular, to Waldir — a brainstorming partner and a friend.

And last but not least, I want to thank my family and friends – as an American writer once said:

You can kiss your family and friends good-bye and put miles between you, but at the same time you carry them with you in your heart, your mind, your stomach, because you do not just live in a world but a world lives in you.

#### Funding

The work that composes this thesis was funded by National Funds through the *FCT - Fundação para a Ciência e a Tecnologia* (Portuguese Foundation for Science and Technology) and by ERDF - European Regional Development Fund through the COMPETE Programme (operational programme for competitiveness) within projects PTDC/EIA-EIA/100035/2008, PEst-OE/EEI/UI0752/2014, FCOMP-01-0124-FEDER-010067 and UID/CTM/50025/2013. Also by the School of Engineering, University of Minho, within project P2SHOCS - Performance Portability on Scalable Heterogeneous Computing Systems and by the PT-FLAD Chair on Smart Cities & Smart Governance. To these entities, I would like to express my sincerest gratitude.

#### Resources

I would like to thank **Kyle Mooney** and other authors for providing the code supporting migration of dynamically refined meshes in OpenFOAM (Chapter 4). I would also like to acknowledge the **Texas Advanced Computing Center** (TACC) at The University of Texas at Austin, and the **SeARCH** computing project at the University of Minho, for providing the HPC resources.

# Numerical Simulations on Heterogeneous Systems: dynamic workload and power management

Abstract. Numerical simulations are among the most relevant and computationally demanding applications used by scientists and engineers. As accuracy requirements keep increasing so does the corresponding workload and, consequently, the demand for additional computing power. HPC systems are thus a fundamental tool to allow for a time effective execution of such simulations; performance maximization is therefore a pertinent and crucial subject of research. Over the last decade HPC has undergone a major shift, resulting on heterogeneous parallel computing systems, which integrate devices with different architectures, exposing different instruction sets, programming and execution models, and ultimately, delivering significantly different performances. This heterogeneity raises a variety of challenges to application developers, such as performance and code non-portability, performance imbalances and disjoint memory address spaces. These challenges not only widen the gap between peak and sustained performance, but also significantly reduce development productivity. Additionally, numerical applications often exhibit dynamic workloads, with unpredictable computational requirements, which, together with associated code divergence and branching workflow, further aggravates the heterogeneity challenge - this is defined as the Two-fold Challenge. The increasing scale in HPC systems also leads to a fast growing power consumption, with power management solutions being of crucial importance. The design of such solutions becomes harder within the two-fold challenge context.

This thesis addresses the Two-fold Challenge in the context of numerical simulations and HPC systems, focusing on optimising sustained performance and power consumption. A variety of mechanisms is proposed and validated across different parallel computing paradigms. These mechanisms include a unified execution and programming model, a transparent data management component and heterogeneity-aware dynamic load balancing and power management systems. The contributions of this thesis are divided into three areas: efficient and effective application development and execution on heterogeneous single-nodes with multiple computing devices, load and performance imbalances in heterogeneous distributed systems and power-performance trade-offs in heterogeneous distributed systems. In order to foster the adoption of proposed mechanisms, some were designed and integrated into a widely used numerical simulation library – OpenFOAM. Experimental results assert the effectiveness of the proposed approaches, resulting on significant gains in performance and reduced power consumption in multiple scenarios.

# Simulações Numéricas em Sistemas Heterogéneos: carga dinâmica e gestão de potência

Resumo. Simulações numéricas são uma das mais importantes e computacionalmente exigentes aplicações usadas por cientistas e engenheiros. A carga computacional destas aplicações é proporcional aos requisitos de precisão da simulação, que por sua vez, têm aumentado significativamente, resultando numa maior exigência a nível de poder computacional. Os sistemas de computação de alto desempenho (High Performance Computing (HPC)) são uma ferramenta fundamental, que permitem executar estas aplicações em tempo útil. Obter o desempenho máximo destes sistemas é portanto uma área de investigação de elevada importância e pertinência. Na ultima década, a computação de alto desempenho tem sido alvo de consideráveis mudanças, resultando em sistemas computacionais paralelos e heterogéneos. Estes sistemas são compostos por dispositivos com diferentes arquiteturas, instruction sets e modelos de programação e execução, resultando em desempenhos significativamente diferentes. Esta heterogeneidade levanta vários desafios, nomeadamente, código da aplicação e desempenho não portáveis entre dispositivos, diferenças de desempenho e espaços de endereçamento de memória disjuntos. Estes desafios, não só aumentam a diferença entre o pico de desempenho e o desempenho obtido, mas também reduzem significativamente a produtividade. Mais ainda, as aplicações numéricas exibem, frequentemente, cargas dinâmicas, cujos requisitos computacionais são imprevisíveis. Este dinamismo, combinado com a divergência do código e com o controlo de fluxo condicional, agrava as complexidades associadas à heterogeneidade do sistema, sendo referido como Two-fold Challenge. O progressivo aumento da dimensão dos sistemas HPC tem também, como consequência, um rápido aumento do consumo de potência. Sistemas de gestão de potência são portanto de extrema importância, no entanto, o desenvolvimento destes sistemas torna-se complexo perante o Two-fold Challenge

Esta tese aborda o *Two-fold Challenge* no contexto de simulações numéricas e sistemas HPC, focando-se na otimização do desempenho e potência consumida. Vários mecanismos são propostos e validados em diferentes paradigmas de computação paralela. Nomeadamente, modelos unificados de execução e programação, sistemas transparentes de gestão de dados e sistemas de balanceamento de carga e gestão de energia baseados na heterogeneidade do sistema. As contribuições desta tese são divididas em três áreas: desenvolvimento e execução eficiente de aplicações em sistemas heterogéneos com um único nó e múltiplos dispositivos, desbalanceamento de carga computacional e desempenho em sistemas heterogéneos distribuídos e compromissos entre desempenho e potência consumida em sistemas heterogéneos distribuídos. De forma a promover o uso dos mecanismos propostos, parte destes foram desenvolvidos e integrados numa conceituada biblioteca de simulações numéricas – OpenFOAM. Resultados experimentais validam a eficácia dos mecanismos propostos, resultando em ganhos significativos de desempenho e redução de potência consumida em múltiplos cenários.

# Contents

Chapter 1 Introduction Context and Motivation, 2 Facing the Challenges, 8 Goals and Contributions, 9 Thesis Structure, 12

# 13

25

Chapter 2 Background

Modern HPC Architectures, 14 Parallel Programming Models, 16 Power Management, 19 Addressing the Challenges, 20

#### Chapter 3

Chapter 4

Heterogeneous Single-node Systems Introduction, 26 Related Work, 28 Proposed Approach, 29 Workload Scheduling, 36 Evaluation Approach, 39 Results, 43 Conclusions and Future Work, 52

# 55

Heterogeneous Distributed Systems Introduction, 56 Related Work, 59 nSharma's Architecture, 60 Results, 65 Conclusions and Future Work, 71

## 73

Chapter 5 Power Scheduling in Heterogeneous Distributed Systems Introduction, 74 Related Work, 76 RHeAPAS, 77 Results, 81 Conclusions and Future Work, 87

89

Chapter 6 Conclusions and Future work Conclusions, 90 Future Work, 92

# Acronyms

| ACPI                                                         | Advanced Configuration and Power Interface         |  |

|--------------------------------------------------------------|----------------------------------------------------|--|

| AMR                                                          | Adaptive Mesh Refinement                           |  |

| AS                                                           | Applied Scientist                                  |  |

| BWU                                                          | Basic Work Unit                                    |  |

| CFD                                                          | Computational Fluid Dynamics                       |  |

| CommC                                                        | Graph Communication Graph                          |  |

| CU                                                           | Computing Unit                                     |  |

| DAG                                                          | Direct-acyclic Graph                               |  |

| DD                                                           | Domain Decomposition                               |  |

| DM                                                           | Decision Model                                     |  |

| DMS                                                          | Data Management System                             |  |

| DLB                                                          | Dynamic Load Balancing                             |  |

| DVFS                                                         | Dynamic Voltage and Frequency Scaling              |  |

| FE                                                           | Finite Element                                     |  |

| FLOPS                                                        | Floating-point Operations Per Second               |  |

| FV                                                           | Finite Volume                                      |  |

| FPGA                                                         | Field-programmable gate array                      |  |

| GFLOP                                                        | <b>S</b> Giga Floating-point Operations Per Second |  |

| GPGPU                                                        | General Purpose GPU                                |  |

| HEFT                                                         | Heterogeneous Earliest Finish Time                 |  |

| HPC                                                          | High Performance Computing                         |  |

| HDS                                                          | Heterogeneous Distributed Systems                  |  |

| HSNS                                                         | Heterogeneous Single-Node Systems                  |  |

| HS                                                           | Heterogeneous Systems                              |  |

| DW                                                           | Dynamic Workload                                   |  |

| DSP                                                          | Digital Signal Processor                           |  |

| ILP                                                          | Instruction Level Paralellism                      |  |

| KNL                                                          | Knights Landing                                    |  |

| MPI                                                          | Message Passaging Interface                        |  |

| OPM                                                          | Online Profiling Module                            |  |

| <b>OpenFOAM</b> Open Source Field Operation and Manipulation |                                                    |  |

| PAS                                                          | Power-Adaptive Scheduler                           |  |

| PM    | Performance Model                                        |

|-------|----------------------------------------------------------|

| RHeAl | PAS Runtime Heterogeneity-Aware Power-Adaptive Scheduler |

| RM    | Repartitioning Module                                    |

| RSD   | Relative Standard Deviation                              |

| SIMD  | Single Instruction Multiple Data                         |

| SIMT  | Single Instruction Multiple Threads                      |

| TDP   | Thermal Design Power                                     |

| TPL   | Task Parallel Library                                    |

| UDP   | Uniform Distribution of Power                            |

# **List of Figures**

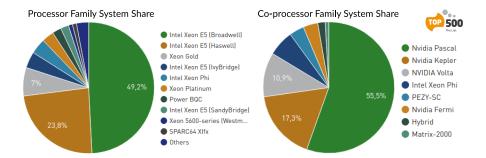

| 1.1  | Processor and co-processor family system share from June 2018 Top500 supercomputer list                                                                                                  | 3  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Some examples of heterogeneous supercomputers in the top                                                                                                                                 |    |

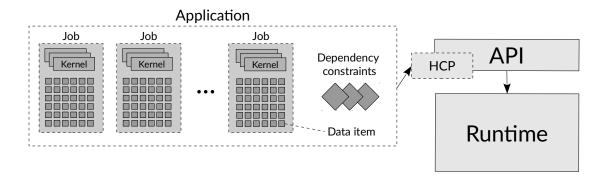

| 3.1  | 60 places of the June 2018 Top500 Supercomputing list Application specification and HCP components. Application jobs and dependency constraints are submitted to the system              | 4  |

|      | by implementing the HCP using the API                                                                                                                                                    | 30 |

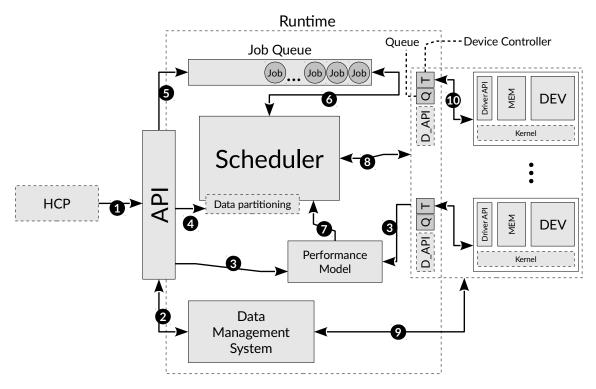

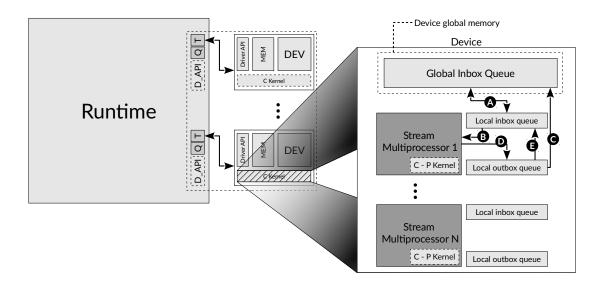

| 3.2  | Runtime architecture and workflow.                                                                                                                                                       | 35 |

| 3.3  | Persistent kernel architecture and workflow.                                                                                                                                             | 39 |

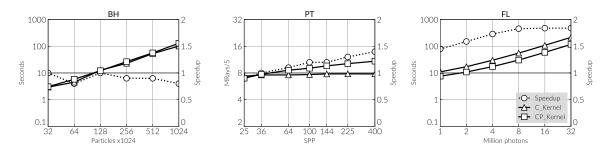

| 3.4  | Performance comparison between C-Kernel and CP-Kernel on<br>a single GPU. Note the left-handed y-axis and x-axis in log scale                                                            |    |

|      | and right-handed y-axis in linear scale                                                                                                                                                  | 44 |

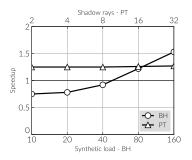

| 3.5  | Load impact in performance, expressed in terms of speedup of<br>the consumer-producer kernel over the consumer one. Num-<br>ber of shadow rays per shading point in PT (upper horizontal |    |

|      | axes) and synthetic load for BH (lower horizontal axes). Note                                                                                                                            |    |

|      | that both horizontal axes are in log scale.                                                                                                                                              | 44 |

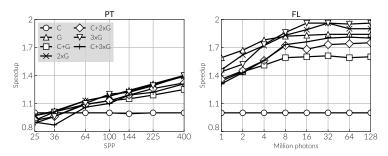

| 3.6  | Performance comparison between consumer kernel and                                                                                                                                       |    |

|      | consumer-producer kernel with multiple-device configurations                                                                                                                             |    |

|      | when scheduling PT and FL irregular workloads. C stands for                                                                                                                              |    |

|      | CPU and G for GPU. Note that horizontal axis is in log scale.                                                                                                                            | 45 |

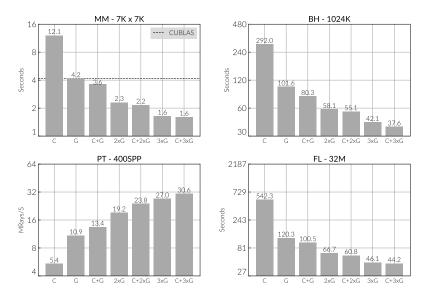

| 3.7  | Performance with multiple-device configurations. A consumer kernel type is used for the MM and BH applications and a                                                                     |    |

|      | consumer-producer kernel in PT and FL. C stands for CPU and                                                                                                                              |    |

|      | G for GPU. Note the vertical axis in log scale                                                                                                                                           | 47 |

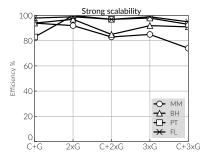

| 3.8  | Strong scalability: heterogeneous efficiency for the four case                                                                                                                           |    |

|      | studies. 7k x 7k matrix for MM, 1024k particles in BH, 400 SPP                                                                                                                           |    |

|      | for PT and 32M photons in FL.                                                                                                                                                            | 49 |

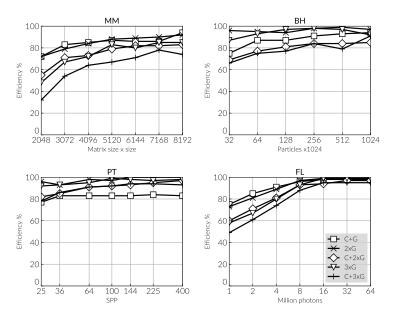

| 3.9  | Heterogeneous efficiency with multiple workloads and                                                                                                                                     |    |

|      | multiple-device configurations. Consumer kernel for MM and                                                                                                                               |    |

|      | BH, consumer-producer kernel for PT and FL. C stands for                                                                                                                                 |    |

|      | CPU and G for GPU.                                                                                                                                                                       | 50 |

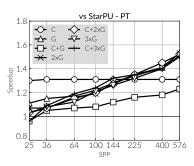

| 3.10 | Path tracing – Speedup of the proposed approach over StarPU                                                                                                                              |    |

|      | with multiple device configurations when scheduling irregular                                                                                                                            |    |

|      | workloads. C stands for CPU and G for GPU. Note that hori-                                                                                                                               |    |

|      | zontal axis is in log scale                                                                                                                                                              | 52 |

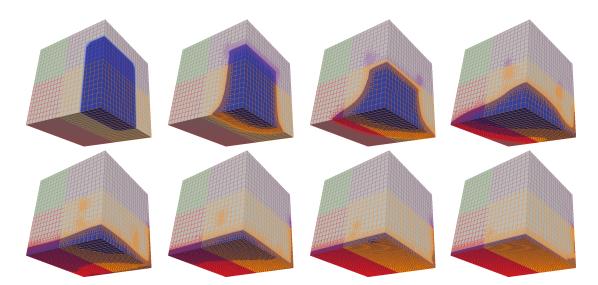

| 4.1        | <i>damBreak</i> geometry and a subset of the simulation result with<br>4 ranks (each color represents the cells assigned to a different<br>rank) and AMR. Cell distribution devised using ParMETIS and                                                                                                                                               |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | default parametrisation.                                                                                                                                                                                                                                                                                                                             | 65 |

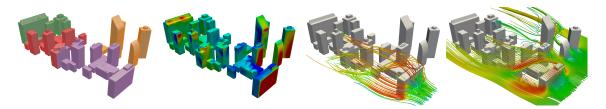

| 4.2        | windAroundBuildings simulation illustration. First plot shows<br>cells distribution over 4 ranks (each color represents the cells<br>assigned to a different rank), second plot illustrates the pres-<br>sure at time-step 200 and the two last plots show examples of                                                                               |    |

|            | velocity stream lines. Cell distribution devised using ParMETIS                                                                                                                                                                                                                                                                                      |    |

|            | and default parametrisation.                                                                                                                                                                                                                                                                                                                         | 65 |

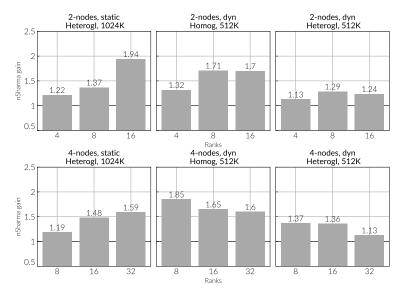

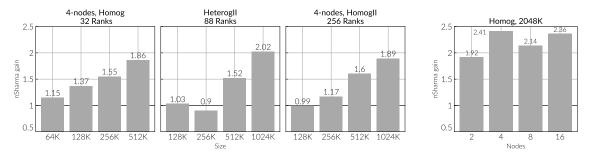

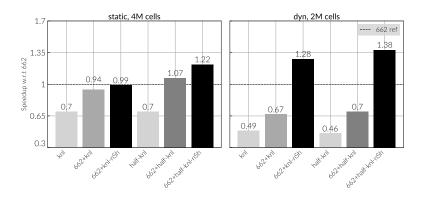

| 4.3        | nSharma gain with SeARCH Homogeneous and Heteroge-<br>neous I                                                                                                                                                                                                                                                                                        | 67 |

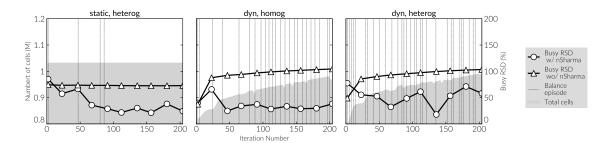

| 4.4        | Busy RSD with and without nSharma for 4 nodes and 32 ranks.                                                                                                                                                                                                                                                                                          | 68 |

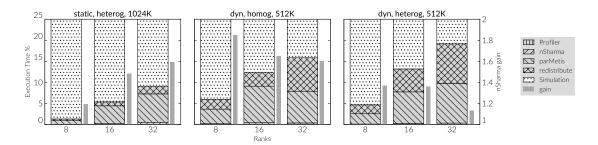

| 4.5        | Execution time percentage breakdown for 4 nodes                                                                                                                                                                                                                                                                                                      | 68 |

| 4.6        | First three plots show an increasing problem size for four 641<br>SeARCH nodes, 662+KNL and four Stampede2 nodes and dy-<br>namic workload. Last plot shows an increasing number of 641<br>nodes using the maximum number of ranks, dynamic workload                                                                                                 |    |

| 4.7        | and about 2 million cells                                                                                                                                                                                                                                                                                                                            | 69 |

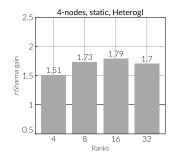

| 4.8        | uration nodes and static workload                                                                                                                                                                                                                                                                                                                    | 70 |

|            | pede2 nodes                                                                                                                                                                                                                                                                                                                                          | 70 |

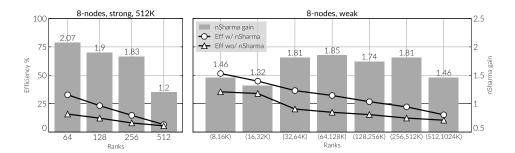

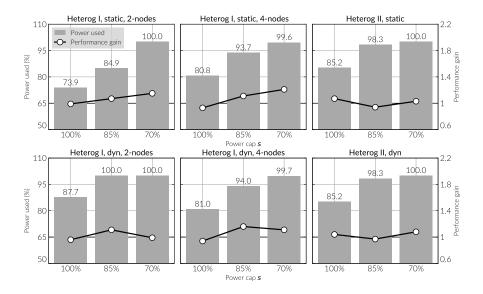

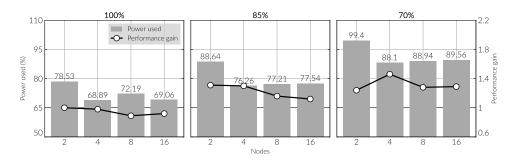

| 4.9<br>5.1 | Speedup in combining a 662 node and a KNL by using nSharma<br>Power used and performance gain for (2 and 4 nodes) Hetero-<br>geneous I and II with static and dynamic workload in SeARCH.                                                                                                                                                            | 71 |

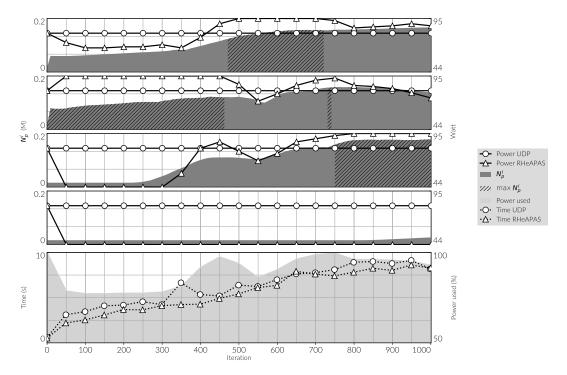

| 5.2        | 512K cells for static 256K cells for dynamic Power assignment and iteration execution time along simulation. $N_p^i$ , in the first four rows y-axis, is according to Equation                                                                                                                                                                       | 83 |

|            | 5.8. 1000 timesteps with 4 homogeneous (641) nodes, dynamic workload and a 85% power budget                                                                                                                                                                                                                                                          | 84 |

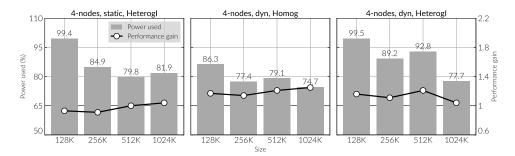

| 5.3        | Increasing number of cells in the x-axis. 85% power budget, 4 nodes, Heterogeneous I with static load, and Homogeneous I                                                                                                                                                                                                                             |    |

|            | and Heterogeneous I with dynamic workload                                                                                                                                                                                                                                                                                                            | 85 |

| 5.4        | Weak scaling based analysis, homogeneous nodes increasing in<br>the x-axis. 512K, 1024K, 2048K and 4096K as number of cells                                                                                                                                                                                                                          |    |

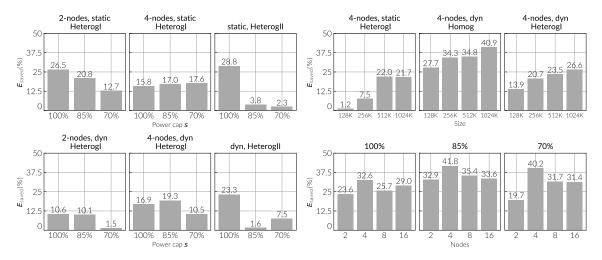

| 5.5        | respectively, and dynamic workload Energy consumption reduced for the same configurations of the previous plots. In the first two rows, 512K cells for static 256K cells for dynamic. 85% limit of power for the third row and the last row is a weak scaling with homogeneous 641 nodes with increasing cells (256K, 512K, 1024K and 2048K) and dy- | 86 |

|            | namic workload                                                                                                                                                                                                                                                                                                                                       | 87 |

|            |                                                                                                                                                                                                                                                                                                                                                      |    |

# **List of Tables**

| 3.1 | Speedup of the consumer-producer kernel over the consumer       |    |

|-----|-----------------------------------------------------------------|----|

|     | kernel with load impact in performance as workload is increased |    |

|     | per BWU in BH and PT                                            | 45 |

| 3.2 | Performance values with multi-device configurations. C stands   |    |

|     | for CPU and G for GPU.                                          | 46 |

| 3.3 | Performance values with multi-device configurations compared    |    |

|     | to a reference version running on a single GPU. PT values dif-  |    |

|     | fer from Table 3.2 because a single shadow ray was used per     |    |

|     | shading point. C stands for CPU and G for GPU                   | 47 |

| 3.4 | Strong scalability: heterogeneous efficiency for the four case  |    |

|     | studies. 7k x 7k matrix for MM, 1024k particles in BH, 400 SPP  |    |

|     | for PT and 32M photons in FL. C stands for CPU and G for GPU.   | 49 |

| 4.1 | Computing systems and system configurations used in evaluation  | 66 |

| 5.1 | SeARCH Computing nodes and system configurations used in        |    |

82

. . . . . . . . . . . . . . . .

# List of Infos

evaluation . . . . . . . . . . . .

| 1.1 | Numerical Simulation by <i>nature.com</i>                             | 2  |

|-----|-----------------------------------------------------------------------|----|

| 1.2 | Clusters, Supercomputers and HPC Systems                              | 3  |

| 1.3 | Application workload types: static, regular, dynamic and irregular    | 6  |

| 1.4 | Computing Unit (CU)                                                   | 8  |

| 1.5 | Contribution I                                                        | 10 |

| 1.6 | Contribution II                                                       | 10 |

| 1.7 | Contribution III                                                      | 11 |

| 2.1 | Applications and Data dependencies                                    | 21 |

| 2.2 | Data-parallel task-scheduling vs Functional task-scheduling $\ . \ .$ | 21 |

| 4.1 | The OpenFOAM Challenge                                                | 58 |

|     |                                                                       |    |

## Chapter

# Introduction

## Contents

|       | Context and Motivation, 2                      |

|-------|------------------------------------------------|

|       | 4-Tier Parallelism, 4                          |

| 1.1.2 | Heterogeneous Systems and Dynamic workloads, 5 |

| 1.1.3 | Power Consumption Challenge, 7                 |

| 1.2   | Facing the Challenges, 8                       |

| 1.3   | Goals and Contributions, 9                     |

| 1.3.1 | Main Contributions, 10                         |

| 1.3.2 | Experimental Context, 11                       |

| 1.4   | Thesis Structure. 12                           |

Civilization is a progress from an indefinite, incoherent homogeneity toward a definite, coherent heterogeneity.

#### Herbert Spencer

In this initial chapter, a detailed discussion on the context and motivation of this thesis is provided. An overview of the state of today's computing systems is presented, together with the identification of a set of challenges that emerged from the way computing technologies evolved. It also introduces a hierarchical taxonomy that categorizes the paradigms of parallel computing. In the final sections, a brief overview of how this thesis will approach the identified challenges is provided, defining the research hypothesis, goals and contributions of this thesis.

## 1.1 Context and Motivation

Numerical computer simulations extend the human capability to acquire knowledge on fundamental aspects of physics. They allow studying the behaviour of complex physical systems that are impractical to assess either by analytical or experimental methods. Weather forecasting, financial market forecasting, medical and health-care development, image synthesis and rendering, aircraft aerodynamics are just some of the examples of a vast set of applications that make use of numerical simulations. The value and accuracy of these simulations are correlated with their workload which has a direct impact on the computational effort. For instance, larger refined models of a city in weather forecasting yield a more accurate and wider weather prediction, a larger pixel sampling and resolution in a physically based rendering algorithm results in higher-quality photo-realistic images. This results in a generalized demand for computing power in order to enable higher quality and complex simulations [1].

#### > Numerical Simulation by nature.com

A numerical simulation is a calculation that is run on a computer following a program that implements a mathematical model for a physical system. Numerical simulations are required to study the behaviour of systems whose mathematical models are too complex to provide analytical solutions, as in most non-linear systems.

Given the computing complexity and volume of the data associated with these applications, their execution times easily achieve the order of days or weeks, largely depending on the computing resources available. High Performance Computing (HPC) systems are a fundamental tool used by scientists and engineers to implement and run numerical simulations as they offer higher levels of computing capabilities. HPC systems performance delivery is fundamentally based on parallel computing and scalability provided by stand-alone sophisticated servers and by large-scale clusters with thousands of compute nodes. Maximizing the extracted performance from these systems is, therefore, a pertinent and crucial subject of research and development.

In the last decades, driven by the surge in computational requirements, HPC systems have been subject to significant change in architectural design and development. Manufacturers consistently increased the CPU transistor count and devised sophisticated approaches to organize chip space in order to further increase performance (e.g. vectorization, superscalar, etc). However, limited by the power wall, chip

#### Clusters, Supercomputers and HPC Systems

**Cluster** is a core architectural concept based on a set of computers connected by a local network providing extended parallel computing capabilities. **Supercomputer** is a large-scale computing infrastructure based on the cluster concept and used in the solving of complex and large scientific problems. **HPC systems** are computing platforms targeted to deliver higher levels of computational power aimed to solve complex computational problems. HPC systems range from standalone compute servers to large-scale supercomputers.

manufacturers adopted new architectures and embraced parallelism within the chip as the mainstream approach to overcome the physical limitations [2], [3]. Multi-core CPUs quickly became ubiquitous as well as sophisticated computing paradigms such as multi-threading.

With the introduction and development of programmable shaders, along with advancements in floatingpoint support, GPUs became able to compute highly-parallel scientific tasks with substantially higher performance than common CPUs due to its many-core architecture. With the introduction of highly productive programming models, such as CUDA and OpenCL, these co-processing devices became general purpose scientific computing devices and ubiquitous across HPC systems. Intel also pursued the manycore co-processing approach with the first Intel Xeon PHI device that consisted in a 48-core chip with wide-SIMD capabilities and x86 compatible. Intel continued to develop these micro-architectures and recently released a new many-core self-hosted <sup>1</sup> device with codename Knights Landing (KNL) with 64 cores.

Figure 1.1: Processor and co-processor family system share from June 2018 Top500 supercomputer list

Sophisticated multi-core CPUs, many-core GPUs and Xeon PHI's are common devices equipped in standalone HPC compute servers and supercomputer nodes. This multitude of devices fundamentally revolutionized the plurality in terms of HPC technology, outsetting the *Heterogeneous Computing Era* [4]. This is clearly observed in Figure 1.1 that illustrates the processor and co-processor family systems share in the Top500 supercomputer list. Compute nodes are heterogeneous as they are composed of devices that are designed with different architectures, using different instruction sets, programming and execution models, and ultimately deliver significantly different performances. Clusters are rendered heterogeneous as

<sup>&</sup>lt;sup>1</sup>the many-core is the main CPU

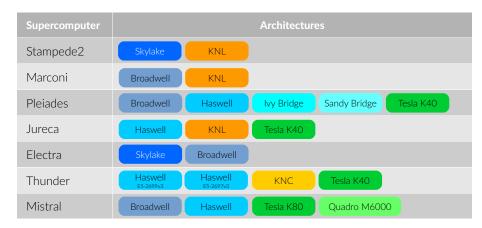

they can be easily extended with nodes with more efficient CPU architectures and new sophisticated coprocessing devices. Figure 1.2 briefly illustrates some examples of heterogeneous supercomputers and their architectures present in the top 60 places of the Top500 supercomputers list<sup>1</sup>. For instance, the *Pleiades* from NASA, is composed by four different Intel architectures and a NVIDIA GPU architecture.

**Figure 1.2:** Some examples of heterogeneous supercomputers in the top 60 places of the June 2018 Top500 Supercomputing list.

### 1.1.1 4-Tier Parallelism

With the adoption of parallelism as the mainstream paradigm to increase performance and considering the current structure of HPC systems, a hierarchical parallel computing structure can be defined using a 4-Tier hierarchical taxonomy:

- **Tier-4** Inter-node parallelism in a distributed memory system where nodes compute concurrently. Each node has its own memory addressing space.

- Tier-3 Intra-node parallelism within a single compute node with multiple compute devices, also known as inter-device parallelism or in some cases hybrid execution where devices (e.g CPU and GPU) compute concurrently. Typically each device has its own memory space.

- Tier-2 Intra-device parallelism, parallelism within device where cores compute concurrently. Memory space is typically shared across cores.

- Tier-1 Intra-core parallelism, a typical example is Single Instruction Multiple Data (SIMD) execution also known as vectorization. In some devices, dedicated registers are used. GPUs also promote SIMD execution using a massive multi-threading approach.

A **Tier-o** could be defined as the Instruction Level Paralellism (ILP) within core considering superscalar execution and instruction pipelining.

<sup>&</sup>lt;sup>1</sup>Note that some heterogeneous supercomputers may have some restriction policies that limit the use of different architectures simultaneously.

## 1.1.2 Heterogeneous Systems and Dynamic workloads

With the embracing of parallelism and with the advent of the heterogeneous era, several challenges emerge that not only affect the application development productivity but also severely impact the extracted performance of today's computing systems. These challenges are further aggravated in the presence of dynamic workload applications such as numerical simulations. This section briefly describes the challenges posed by parallel heterogeneous systems and in particular the impact of combining them with dynamic workloads.

#### The Heterogeneity Challenge

A cluster can be fairly easily extended by adding more compute nodes with similar architectures, but often from newer and more sophisticated generations offering more computing capabilities. This same extensibility, however, renders the system heterogeneous in the sense that different generations of hardware with different levels of performance coexist across nodes leading to **performance imbalances**. These performance imbalances are also originated from the diversity of devices that constitute a node. Resource idling and underutilization along with poor scalability are the major consequences of an imbalanced system [5], [6].

In the presence of multiple devices with different architectures, one of the major challenges is the **performance non-portability** across devices. For instance, an application optimized for the CPU may deliver far less performance in a GPU and vice-versa [7]. This is due to the different execution models and associated device architecture details that are designed to address different types of workloads. Programmers need to re-design their applications in order fully benefit from each device computing capabilities.

In devices with **disjoint memory address spaces** – such as GPUs and other co-processors – application data must travel through a limited bandwidth bus (PCI-Express), which results in a potential performance bottleneck. Data transfers must be explicitly managed and minimized for consistency and efficiency purposes[8]. This not only affects performance, but significantly reduces productivity. Moreover, these devices are typically used with libraries and programming tools (CUDA, OpenMP, Intel TBB, etc) developed by each of the different manufacturers that reflect the differences in execution models and architectures of their devices. Programmers need to comply with these divergent programming models resulting in **non-portable code**.

#### Dynamic Workload Challenge

Most numerical computer simulations are data-parallel. Data-parallel applications distribute data to compute units that apply some computational operation (or kernel) on the assigned data in parallel. Data is typically defined by a set of work units that represent some entity, object or modelling element, for instance, a cell of a discretized domain in Finite Volume (FV) Computational Fluid Dynamics (CFD) simulations [9].

Data-parallel applications can be classified in two types — static or dynamic. In **static** (also known as regular) applications, the workload is the same for the entire execution. The number of work units is known *a priori*, typically defined in the start of the application and divided across computing resources or submitted to a queue for processing. These applications exhibit a constant and predictable computational effort requiring simpler scheduling and partitioning heuristics in order to be efficiently distributed across computational resources.

With **dynamic** applications, each of the data elements can be subdivided, merged or generate more work units, rendering the computational effort unpredictable and irregular [10], [11]. The distribution of dynamic workloads across parallel computing resources becomes a far more complex challenge due to an unpredictable number of work units and/or an unknown number of operations per work unit. If an uniform distribution of workload is applied, each compute unit will receive the same amount of work units. However, since each work unit may require an **arbitrary amount of computational effort**, the system will be imbalanced and resource idling occurs.

A **sub-type** of dynamic applications can be defined as **irregular applications** when the generation of work results in **code divergence and branching workflow**. These applications will significantly hinder the performance in many-core devices, such as the GPU [12]. The massively threaded execution model favours well defined and regular code, but with irregular workloads, arbitrary (uncoalesced) memory accesses and unpredictable complex execution patterns will potentially result in significant performance losses.

#### Application workload types: static, regular, dynamic and irregular

Data-parallel applications can be classified in two main types – static or dynamic. **Static applications**, also known as **regular applications**, exhibit a constant and predictable computational workload across the whole compute time. The number of work units is known *a priori*, typically defined in the start of the application and divided across computing resources or submitted to a queue for processing. Examples of static data-parallel applications are matrix multiplications and decompositions, where the number of elements is known and the operations per element can be determined and thus so the global number of operations. CFD simulations with static meshes can also be considered static applications as they require a uniform computational effort along the runtime.

With **dynamic applications** the workload is generally unpredictable and irregular across the runtime. Each of the data elements can be subdivided, merged or generate more work units resulting in an unpredictable amount of computational effort associated with each of the work units. For instance, a CFD simulation with Adaptive Mesh Refinement is considered a dynamic application since each cell can be recursively subdivided or merged along the simulation depending on fluid flow or other properties. A sub-type of dynamic applications can be defined as **irregular applications** when the generation of work results in code divergence and branching workflow. These applications are typically characterized by irregular data structures, irregular control flow and/or irregular communication patterns with uncoalesced memory accesses. An example of an irregular application is the Monte-Carlo physically based rendering engine. The workload associated with processing a pixel is unpredictable since both direction and length of the path of the pixel ray are stochastically generated and scene dependent.

Yet, dynamic data-parallel applications constitute the largest percentage of numerical computer simulations, not only because they are typically associated with complex real-world data and models but also because they are expressed using irregular algorithms such as random walks [13], [14], graph and sparse matrix algorithms [15], [16], particle simulations [17]–[19], meshing techniques [9], [20], among others. The pertinence of these applications renders the study and development of workload scheduling algorithms crucial.

#### The Two-fold Challenge

As discussed in the two previous sections, Applied Scientists (ASs) rely on HPC systems to perform numerical simulations. These systems, however, are heterogeneous and pose a number of challenges that need to be addressed in order to be efficiently used. Furthermore, numerical simulations are prone to exhibit a dynamic and unpredictable workload behaviour that is hard to be efficiently distributed and executed. The combination of these two computing features results in a further enlargement of the complexity of the individual challenges identified — this is defined as the **Two-fold Challenge**.

The workload that needs to be scheduled is now dynamic and unpredictable, which aggravates the performance imbalance issue among the heterogeneous computing units. Computing units with less performance and already causing imbalance may sustain a workload increase which will substantially increase the idling of faster units. Dynamic generation of work will also promote code divergence and branching which aggravates the performance portability issue. In the presence of multiple devices, accounting for different execution models becomes a more complex task when computing divergent and branched workflow. Data management becomes also non-trivial since the data required by devices is potentially arbitrary.

Indeed, these two computing features – resource heterogeneity and dynamic workload – are relevant topics but boost each other and correlate in hindering productivity and performance extraction. Notice that all these challenges are addressed either by a computer scientist or an AS. The latter is a non-expert programmer that usually has basic programming skills and computer science knowledge. Design and development of mechanisms to counter the challenges posed by the combination of these features, specifically, in relevant applications like numerical simulations, is, therefore, a pertinent research area.

### 1.1.3 Power Consumption Challenge

The increasing scale of HPC systems leads to a **fast-growing power consumption** that is becoming one of the major concerns in developing and maintaining these systems [21]. The cost of energy required to power a supercomputer tends to surpass the cost of the system itself, resulting in a huge economic impact but also the inherent consequences in terms of environment. Power management becomes of crucial importance where HPC solutions – either hardware and software – need to be re-evaluated in

terms of power-efficiency [22]. Since computing devices are based on electrical integrated circuits, power consumption has a close correlation to performance. A power management system must seek to reduce power consumption but also maintain acceptable levels of performance.

However, **power management becomes a far more difficult** challenge in systems exposed to the two-fold challenge. Each of the multiple devices that co-exist in a system may exhibit different power consumptions and different performances. Any strategy to reduce power consumption becomes non-trivial where the power manager needs to account for the impact of power changes and the subsequent impact on performance that is particular to each device. In the presence of dynamic workloads, designing of such strategy becomes even more complex given the unpredictability of the workload generated by the application.

# 1.2 Facing the Challenges

Performance imbalances are caused by a plurality of devices and architectures and by the dynamic nature of the workload associated with many applications, such as the numerical simulations addressed throughout this thesis. These issues can be addressed by rising awareness on each Computing Unit (CU) performance using **performance models** and combine that information with runtime **Dynamic Load Balancing (DLB)**. These features will provide heterogeneity-aware workload partitioning and redistribution that will assign and migrate work according to performances and current system load. This will minimize resource idling thus increasing utilization and scalability.

#### Computing Unit (CU)

A Computing Unit is an abstraction used in this document that represents a device or a set of devices that perform computation. For instance, a single CPU core, a CPU, a GPU, a cluster compute node, etc.

The diversity of devices' computing models also causes the application implementation and optimization to be non-portable. Both performance optimizations and code implementation can not be efficiently and transparently applied to multiple different devices. In order to address this issue, an **unified execution and programming model** can be proposed. The unified execution model will account for the different particularities of each device and provide an execution workflow that is both transparent to the user and accounts for the code divergence and irregular workflow of dynamic applications. This will increase productivity and will try to improve the performance of devices that do not favour dynamic and irregular applications. The unified programming model should be device agnostic and hide code primitive details from the programmer, fundamentally increasing productivity.

The disjoint memory address spaces of co-processors results in explicit data management for consistency and efficiency purposes. By designing and integrating a **data management system**, transparent data transfers can be performed and optimization mechanisms such as locality-aware scheduling can be applied. Data management is accessed by an API that is part of the unified programming model, therefore providing device agnostic data management and further increasing productivity.

Power consumption is one of the most concerning aspects in today's computing systems. Heterogeneous systems and dynamic workloads further hamper the power management challenge. A **dynamic and adaptive heterogeneity-aware power assignment** is thus required that will account for dynamic changes of the workload and perform power assignment decisions while weighing performance impact. The power decisions can be supported by a **performance model combined with a power model** resulting in a unified power-performance efficiency mechanism.

# 1.3 Goals and Contributions

The research hypothesis put forward by this thesis is that the challenges raised across the 4-Tiers of parallelism by the heterogeneity of resources, the dynamic nature of the computational workload and the huge power consumption of current HPC systems can be effectively addressed by a thoughtful combination of the above described mechanisms. In particular:

- a **unified execution and programming model** for heterogeneous systems, fully integrated with a transparent **data management system**, will effectively address the **performance portability** challenge, while simultaneously **increasing programming productivity** and promoting utilization of HS among AS;

- dynamic load balancing and heterogeneity aware scheduling, properly grounded on robust and light weight performance models, will address the above identified two-fold challenge, optimizing resource utilization and orchestration towards minimization of application execution time;

- appropriate heterogeneity aware power management mechanisms can effectively limit power consumption while increasing performance when compared with an uniform distribution of the available power budget.

The major goal of this thesis is thus to design, integrate and assess these techniques and provide tools to efficiently and productively develop numerical computer simulations in state of the art HPC systems. The contributions of this thesis cover different systems combined with different applications and address their issues in a scientific and engineering perspective by improving and integrating existing techniques. The following section briefly introduces the main contributions and a detailed discussion is provided in the following chapters.

### 1.3.1 Main Contributions

The contributions of this thesis are divided in three main areas, each targeting a different tier or set of tiers. Each area tries to address a set of challenges that are common to a particular goal and system resource configuration. The main contributions of this thesis are as follows:

Handling Heterogeneous Single-Node Systems (HSNS) The challenges in single node multi-device systems (Tier-3, 2 and 1) are addressed by proposing a unified task-based programming and execution model tailored to efficiently execute data-parallel regular and irregular applications. The integration of persistent kernels is proposed as an intra-device scheduling mechanism along with transparent data partitioning and a device agnostic programming model. The proposed mechanisms are implemented and evaluated with multiple applications and various configurations of CPUs and GPUs. A direct comparison to a state-of-the-art framework is also performed.

#### Contribution I

This contribution that is supported by a scientific paper published in the *Parallel Processing Letters* journal published by *World Scientific*.

R. Ribeiro, J. Barbosa, and L. P. Santos, "A Framework for Efficient Execution of Data Parallel Irregular Applications on Heterogeneous Systems", Parallel Processing Letters, vol. 25, no. 2, p. 1550004, Jun. 2015. DOI:10.1142/S0129626415500048

Runtime heterogeneous-aware load manager for Heterogeneous Distributed Systems (HDS) This contribution evaluates the combination of a DLB system with an application-oriented performance model as a mean to increase resource utilization in performance and workload imbalanced systems. The contribution targets distributed-memory systems (Tier-4) and the designed approach is directly integrated and evaluated in a widely used CFD library (OpenFOAM). It is based on a definition of a Performance Model combined with a decision model that performs educated decisions on how to assign data parallel workload, converging to a balanced computational effort and thus increasing resource utilization. Evaluation is performed across multiple combinations of static and dynamic workload with homogeneous and heterogeneous resource configurations.

#### Contribution II

This contribution is supported by a scientific paper published in the proceedings of the conference *International Conference on Computational Science - ICCS 2018*, part of the *Lecture Notes in Computer Science* book series by *Springer*.

R. Ribeiro, L. P. Santos, and J. M. Nóbrega, "nSharma: Numerical Simulation Heterogeneity Aware Runtime Manager for OpenFOAM", in Lecture Notes in Computer Science, Springer International Publishing, 2018, pp. 429–443, volume 10860. DOI:10.1007/978-3-319-93698-7\_33

Runtime heterogeneous-aware power-adaptive scheduler for HDS Power management is expressed as an optimization problem in order to improve power efficiency and performance in power-limited scenarios. The proposed model is formulated based on two merged objectives: power consumption minimization and performance maximization. Heterogeneity awareness is provided by a performance model and power assignment decisions are adaptively performed at runtime. The approach is evaluated with CFD simulations with dynamic workload running on HDS (Tier-4 parallelism, e.g. multiple CPU generations and KNL nodes). Power consumption reduction and performance behaviour are discussed as well as assessments on energy consumption.

#### Contribution III

This contribution that is supported by a scientific paper published in the proceedings of the conference *International Conference on High Performance Computing & Simulation - HPCS 2018.*

R. Ribeiro, L. P. Santos, and J. M. Nóbrega, "Runtime heterogeneous-aware power-adaptive scheduling in OpenFOAM", in 2018 International Conference on High Performance Computing & Simulation (HPCS), 2018.

### 1.3.2 Experimental Context

This work's hypothesis, goal and contributions are clearly presented throughout Section 1.3. The focus is on heterogeneous parallel computing systems and on the efficient and productive development and execution of numerical computer simulations. There is, however, a major technological shift on the experimental contexts used to validate the proposed hypothesis between the first and the remaining two contributions as identified in Section 1.3.1. The former proposes a specific framework for the development and execution of irregular applications on heterogeneous systems. This framework was conceived and developed within the context of this thesis and requires applications to be developed in compliance with the proposed programming and execution model. The latter contributions propose two plugins written in C++ that integrate onto OpenFOAM in a transparent manner for the OpenFOAM application developer. The reason for this shift in the experimental approach is very pragmatic. As the work progressed from its very early initial stages the team engaged on a collaboration with the University's Institute of Polymers, whose researchers often use OpenFOAM over parallel systems to solve CFD-related problems. It was felt by all that **this thesis' results could be useful for this community**, in particular if the proposed techniques could be applied in a straightforward (eventually transparent) manner. A decision was therefore made to adopt OpenFOAM as the experimental use case.

OpenFOAM is a large and complex CFD simulation framework, with extensions and plugins developed on an open source approach by many practitioners, widely distributed both geographically and institutionally. Adapting OpenFOAM (or a subset) to the initially proposed heterogeneous framework would be an unfeasible task. The reason for this is essentially based on some of the principles that defined the initial framework. These principles resulted in specific application requirements that OpenFOAM does not meet out-of-the-box (such as loosely-coupled data-parallel execution). On the other hand, developing OpenFOAM specific plugins (as is the case of nSharma and RHeAPAS, see Chapters 4 and 5) was deemed feasible, although complex, and their seamless integration with OpenFOAM promotes their adoption by OpenFOAM application developers. This was therefore the path followed throughout this thesis second and third contributions. The author believes that this technological choice has no impact on the scientific validity of the presented findings, with the added benefit of facilitating knowledge transfer from computer science researchers to parallel CFD simulations users.

## 1.4 Thesis Structure

This thesis document is organized in six chapters, two for introductory content and background, three for main contributions and a final concluding chapter.

- Chapter 1 Introduction This chapter provides the context and motivation of this thesis and identifies some of the challenges posed by heterogeneous systems. It also defines the thesis hypothesis and outlines its contributions.

- **Chapter 2 Background** An overview of hardware and software standard solutions is discussed, including a straightforward categorization of modern HPC architectures, followed by the most commonly used APIs and developing tools to work with them. The final section discusses the main issues with these technologies in the context of heterogeneous parallel systems and how they can be addressed.

- **Chapter 3 Heterogeneous Single-node Systems** This chapter describes the first contribution of this thesis where an approach to address the challenges emerged from single-node heterogeneous parallel systems are addressed.

- Chapter 4 Heterogeneous Distributed Systems An approach to tackle the challenges posed by multinode heterogeneous systems is proposed. The proposed mechanisms are essentially based on a dynamic load balancing technique, designed to handle dynamic workloads in systems with performance imbalances across computing nodes.

- Chapter 5 Power Scheduling in Heterogeneous Distributed Systems This presents the third and last contribution, focusing on the power management challenges of heterogeneous distributed systems. It proposed a heterogeneity-aware power-adaptive scheduler based on the solving of an optimization problem. It is recommended to read the Chapter 4 before this chapter.

- **Chapter 6 Conclusions and Future work** General conclusions are provided asserting the successful validation of the thesis hypothesis. The future work is also discussed, where a new model is proposed for development and assessment.

## Chapter

# Background

## Contents

- 2.1 Modern HPC Architectures, 14

- .1.1 Multi-core CPUs, 14

- 1.2 Many-core CPUs and Co-processors, 15

- 2.1.3 GPUs, 16

- 2.2 Parallel Programming Models, 16

- 2.3 Power Management, 19

- 2.4 Addressing the Challenges, 20

This chapter provides a brief overview of hardware and software architectures, including standards and manufacturer tools. It provides a straightforward categorization of modern HPC architectures, followed by the most commonly used APIs and developing tools to work with them. The focus this chapter is on technology that is actually used in today's systems. The final section discusses the main issues with these technologies in the context of heterogeneous parallel systems and how they can be addressed. Detailed related work will be discussed in each of the contribution chapters.

# 2.1 Modern HPC Architectures

Modern HPC systems are composed by a plurality of devices that can be categorized in three main architectures: multi-core CPUs, many-core CPUs and many-core co-processors (which include GPUs). These devices are used both by single node HPC systems or across nodes of a cluster. Single node systems are typically composed by one or more multi-core CPUs and in multiple cases, a high number of co-processors (e.g. NVIDIA DGX-1 with 8 GPUs). The nodes that compose any of the systems in the Top500 [23] list are composed of one or more devices from one or more of these categories.

### 2.1.1 Multi-core CPUs

Multi-core CPUs are designed to be as general purpose as possible. Manufacturers try to develop and enhance CPUs based on complex trade-offs in order to efficiently compute the widest possible range of applications. This results on a chip endowed with extremely complex features but, as a consequence, limited parallelism. Looking at the list of supercomputers, Intel has the larger processor share followed by IBM (PowerPC) and Fujitsu (SPARC). The most recent Intel micro-architecture already used in some systems is codenamed *Skylake*.

*Skylake* chips were introduced in mid-2017, built with 14nm with a core count from 4 to 28<sup>1</sup> with Intel's Hyper-threading technology resulting on 8 to 56 virtual processors. With base operating frequencies ranging from 1.6 GHz to 3.7 GHz and a Thermal Design Power (TDP) between 60W and 240W<sup>2</sup>, these devices perform out-of-order execution with 14 to 19 pipelining stages, branch-prediction, speculative and superscalar execution. The chip also includes three levels of associative cache with more than 1MB per core for the second and third level. Each core is equipped with multiple scalar and vector arithmetic units that provide SIMD operations, which in this latest architecture version has been extended to 512-bit registers (AVX-512). In terms of theoretical performance, the Skylake based Intel Xeon Platinum 8160, for instance, has peak double precision of about **1612 Giga Floating-point Operations Per Second (GFLOPS)**

$<sup>^{1}</sup>$ typically in high-end servers such as supercomputer nodes, chip versions with 24 to 28 cores are used

<sup>&</sup>lt;sup>2</sup>high-end versions have an average of 160W

1.

To get an insight on the performance differences across older multi-core CPUs that still coexist in the same system, the NASA *Electra* supercomputer, for instance, is composed of multiple *Skylake* nodes together with *Broadwell* nodes. The *Broadwell* nodes are composed of Intel Xeon *Broadwell* E5-2680 v4 CPUs (launched in Q1 2016) with 14 cores, 2.4 GHz of base frequency and two 256 bit arithmetic vector units, resulting in **537,6 GFLOPS**<sup>2</sup>.

## 2.1.2 Many-core CPUs and Co-processors

Intel Xeon Phi, formerly known as Intel Many Integrated Core, is a family of x86-compatible many-core devices targeting high-performance massively parallel computing by devoting more transistors to a higher number of simpler cores.

The first production model, still present in multiple HPC systems, is an external device connected to the main system by a PCI-Express bus. Its micro-architecture is codenamed Knights Corner and provides a core count ranging from 57 to 61 cores with an hyper-threading of 4 and from 6 to 16GB of dedicated memory. They operate between 1.0 to 1.2GHz of base clock frequency with most versions exhibiting a TDP of 300W. Cores are connected using a ring topology and each core is based on a modified version of an Intel Pentium Core with two levels of cache and 512-bit vector operations. The theoretical peak performance of a Intel Xeon Phi SE10P is **1073 GFLOPS**<sup>3</sup>.

The second generation of the Xeon Phi architecture is codenamed Knights Landing and was deployed as an external board but also as a standalone self-hosted CPU. They are still targeted for massively parallel computing however they can be configured without any other main device. These devices pack a slight increase in core count from 64 to 72 cores and also an increase in base frequency delivering 1.3 to 1.5GHz of clock speed. The core arrangement is slightly more sophisticated where the modified Intel Atom based cores are organized in tiles interconnected by a 2D mesh. The chip also contains 8 new banks of high bandwidth memory – known as Multi-Channel DRAM (MCDRAM) – of 16GB each. Communication approach between tiles and the use of the MCDRAM can be configured at boot time with different modes that introduce some flexibility in exploiting chip performance. The theoretical peak performance of a Intel Xeon Phi 7250 is **3046 GFLOPS**<sup>4</sup>.

<sup>&</sup>lt;sup>1</sup> 2.1 (GHz) x 24 (cores) x 512/64 (DP AVX) x 2 (FMA units) x 2 (FMA); frequency of AVX units is variable, so actual theoretical performance may be slightly different

<sup>&</sup>lt;sup>2</sup> 2.4 (GHz) x 14 (cores) x 256/64 (DP AVX) x 2 (FMA units) x 2 (FMA))

<sup>&</sup>lt;sup>3</sup>1.1 (GHz) x 61 (cores) x 512/64 (DP AVX) x 1 (FMA unit) x 2 (FMA)

<sup>&</sup>lt;sup>4</sup>1.4 (GHz) x 68 (cores) x 512/64 (DP AVX) x 2 (FMA units) x 2 (FMA)

## 2.1.3 GPUs

GPUs dominate the share in Top500 co-processors with NVIDIA as the main manufacturer. NVIDIA GPUs are mostly external devices connected through PCI-Express bus and dedicated memory. Most of the transistors are devoted to data-parallelism providing a Single Instruction Multiple Threads (SIMT) execution and programming model.

The chip is composed of a set of multiprocessors that create, schedule and execute groups of threads called *warps*. Each multiprocessor contains multiple execution cores and special function units that will concurrently execute the instructions of the warp. The programming model defines a grid of threads which is divided into blocks which in turn are internally organized into warps<sup>1</sup>. In a typical implementation of a GPU application, each thread is associated with a data-parallel work unit and is then executed in an instruction lock-step with the other threads in the warp<sup>2</sup> in a SIMD way. This architecture differs from vector processing in the sense that each thread execute its own instruction allowing programmers to write thread-level parallel code for independent threads<sup>3</sup> [24].

Contrary to multi-core CPUs, there is no branch-prediction nor speculative execution, these devices are designed for maximum throughput by efficiently managing thousands of threads and resorting to memory latency hiding mechanisms (e.g. fast context switching). The latest most commonly available versions of NVIDIA chips are based on the Pascal micro-architecture. For instance, the Tesla P100 has a total of 3584 (simple) cores, 16GB of dedicated memory and operating at a base frequency of 1.2GHz resulting in a TDP of 250W. According to the manufacturer, it has **5300 GFLOPS** of peak double precision performance.

These are the most commonly used devices in HPC but several others architectures coexist contributing to the heterogeneous ubiquity, such as AMD multi-core CPUs, AMD GPUs, Xilinx and Altera Fieldprogrammable gate arrays (FPGAs), Texas Instruments Digital Signal Processors (DSPs), among others.

# 2.2 Parallel Programming Models

Shared memory and distributed memory are two base model abstractions commonly referred to in parallel programming [25]. **Shared memory** allows multiple computing units to access the same memory space, using it for communication purposes and data sharing. This model is typically used with multi-core and many-core CPUs along with multi-threaded programming where each thread has access to node system memory. Since data is shared across threads, data consistency is maintained by the programmer using

<sup>&</sup>lt;sup>1</sup>warps are a hardware scheduling unit, not part of the programming model

<sup>&</sup>lt;sup>2</sup>in recent architecture, like NVIDIA Volta, independent thread scheduling is allowed where a program counter and call stack are maintained per thread.

<sup>&</sup>lt;sup>3</sup>a thread within warp with a different instruction from the other threads will diverge and execute its instructions while the others wait

data concurrency primitives provided by the programming tools.

**Distributed memory** is typically associated with clusters where each of the nodes has its own physically separated memory space. Communications are performed explicitly using programming primitives that transfer data between nodes using a communication protocol. Since nodes are connected by a network, all data transfers and synchronization signals travel through the network. The distributed memory concept may also be applied to multiple GPUs and other co-processors on the same node, each having its own memory space. Communications are typically performed over a PCI-Express bus and it is the programmer responsibility to ensure data consistency and synchronization orchestration. However, for simplification purposes, in the scope of this document distributed memory systems will always refer to clusters with network node inter-connections.

The following sections provide a brief overview of the APIs that are considered of standard and wide use when developing parallel numerical simulations in HPC systems. These development tools originate either from standards defined by committees of major hardware and software vendors or proposed by individual ones in order to use their devices.

## Parallel APIs

In distributed memory systems, the **MPI** [26] standard is the main-stream tool to develop parallel applications. MPI defines an API that allows for orchestration and communication between processes that are hosted in different nodes and/or in the same node. The API provides point-to-point and collective communication primitives that essentially include data transfers and synchronization mechanisms. It is designed basically for the distributed memory paradigm where each MPI process (also known as rank) has its own memory space and it is responsible to handle its own data and execution flow. In a pure-MPI application, each MPI rank will be bond to a core resulting in multiple ranks per node. This mapping can be performed automatically or explicitly controlled by the programmer using process affinities. MPI can also be used in order to perform concurrent execution among multi-core CPUs and many-core co-processors. The Xeon Phi Knights Corner runtime time system allows the MPI library to launch processes allocated within the device and run applications concurrently in a distributed memory approach.

With multi-core and many-core devices, the shared memory approach is typically used and combined with multi-threaded processing. High-level APIs such as **OpenMP** [27] are widely used where the programmer by the means of compiler directives can specify portions of code that are due to run in parallel. OpenMP is then responsible to transparently create and manage threads using a master-slave threading approach. The API will create a specified or automatically detected number of threads and assign each one to a core<sup>1</sup>. **Intel TBB** [28] is a more recent shared-memory library with an increasing adoption that provides

<sup>&</sup>lt;sup>1</sup>thread-core affinity can also be specified

a more robust and feature-rich parallel library. It provides concurrent data structures, synchronization features, task scheduling, among others. **Cilk Plus** [29] and **Microsoft Task Parallel Library (TPL)** [30] are similar libraries, however, Cilk Plus support has been recently deprecated by Intel and TPL is specific to Microsoft .NET technologies. Lower level APIs can also be used to perform thread level parallelism such as **PThreads** [31], **Boost C++** [32] and **C++11 Standard Libraries**<sup>1</sup> [33].

NVIDIA GPU applications are typically developed using the computing platform **CUDA** [24] which provides a compiler, runtime API and other developments tools. The application is developed using extensions to C/C++ where the programmer defines data transfer policies and functional routines – known as kernels – to be executed by the device and a computing resource requirement specification – all using explicit code tags. A kernel call will create a grid that is subdivided into blocks of threads, both grid and a block can be organized in 1,2 and 3D abstractions. Each thread has a local memory and each thread block has an on-chip shared memory space accessible to all threads in the scope of the block. All threads have access to the device global memory.

GPUs as co-processors have their own memory, which means data to be computed must be migrated from host to device memory through PCI-Express channels. Up until the latest Pascal micro-architecture, data consistency and memory fault between host and device was explicitly managed by the programmer. With the advent of the Pascal architecture in 2016, a transparent memory page-fault system was introduced providing automatic data consistency and migration between host and devices.